|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Multi-cycle control:

microprogram |

|

|

|

|

|

|

|

Microprogram

implementation: ROM or PLA |

|

|

|

Each microinstruction has

address, represents 1 clock cycle |

|

|

|

Selection of next

instruction |

|

|

|

|

Increment address: seq |

|

|

|

|

Begin executing next MIPS

instruction: fetch |

|

|

|

|

Jump to microinstruction

based on control input: dispatch |

|

|

|

|

Table contains addresses

of jump targets |

|

|

|

|

Indexed by control inputs |

|

|

|

|

|

|

Multiple tables indicated

by value i in sequencing field |

|

|

|

Blank fields |

|

|

|

|

|

|

|

Functional unit or write

control not asserted |

|

|

|

|

MUX: don't care |

|

|

|

|

|

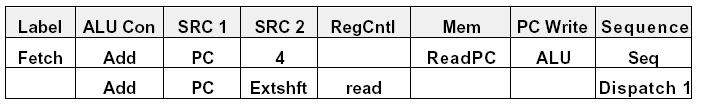

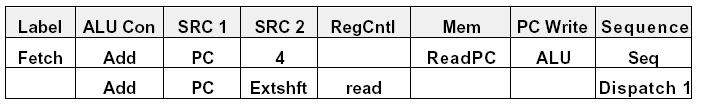

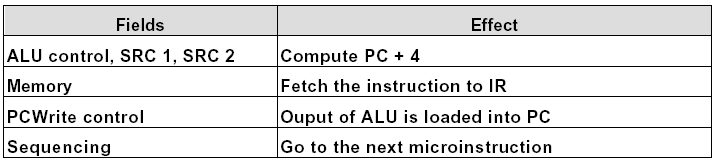

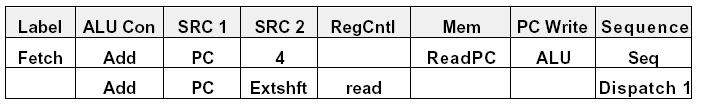

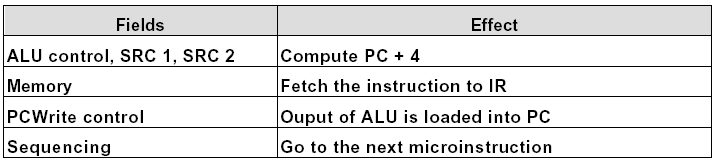

Example: instruction

fetch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

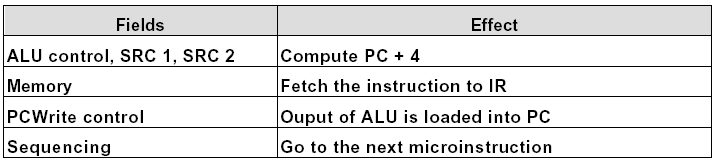

First microinstruction: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

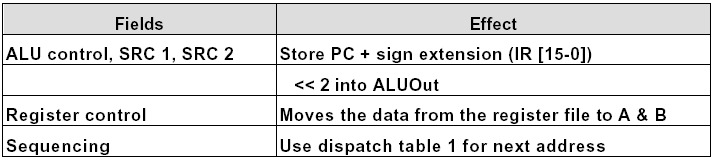

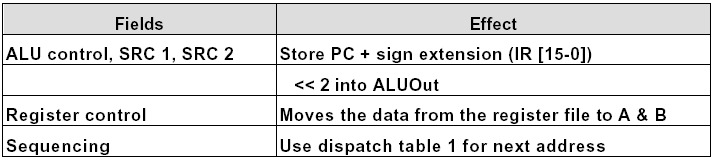

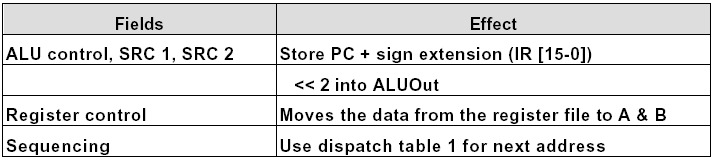

Second microinstruction: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Similar sets of

microinstructions for: |

|

|

|

|

memory access

(load/store) |

|

|

|

R-type instructions |

|

|

|

branch |

|

|

|

jump |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|