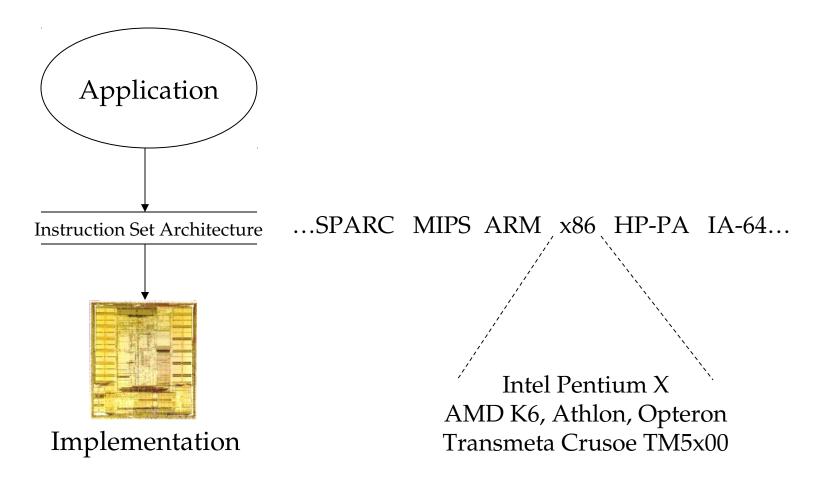

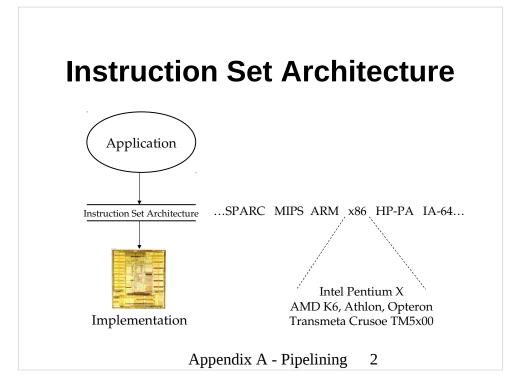

# **Instruction Set Architecture**

# **Instruction Set Architecture**

Strong influence on cost/performance

New ISAs are rare, but versions are not

- 16-bit, 32-bit and 64-bit X86 versions

Longevity is a strong function of marketing prowess

# **Traditional Issues**

- Strongly constrained by the number of bits available to instruction encoding

- Opcodes/operands

- Registers/memory

- Addressing modes

- Orthogonality

- 0, 1, 2, 3 address machines

- Instruction formats

- Decoding uniformity

## Introduction

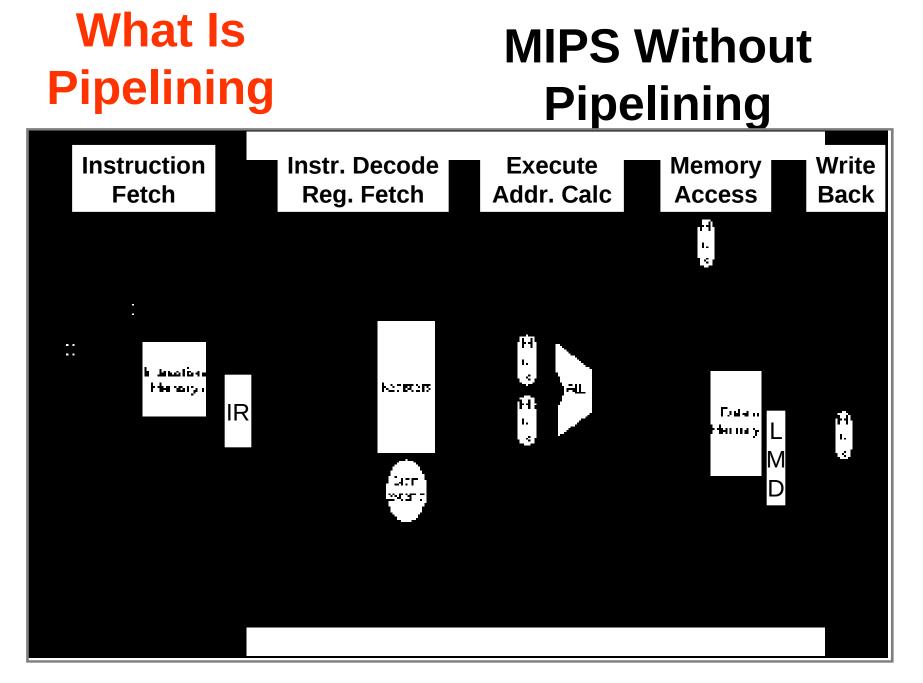

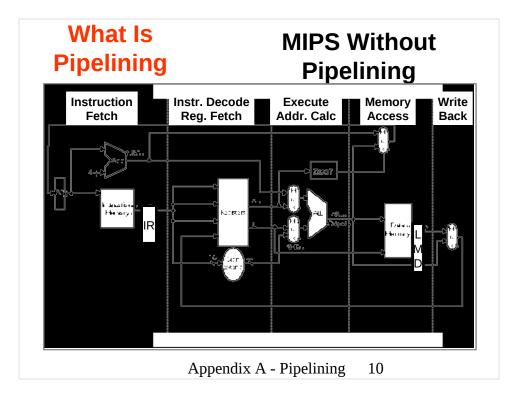

#### A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

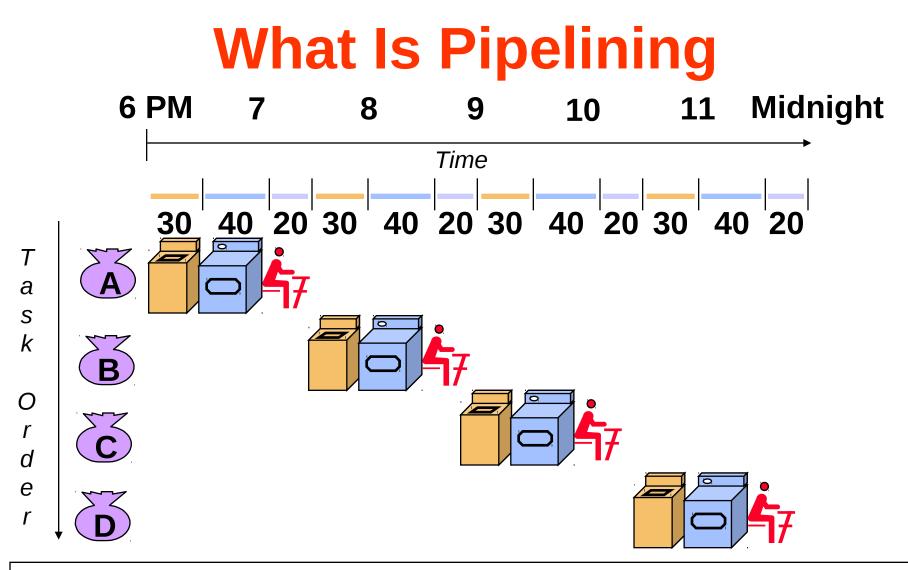

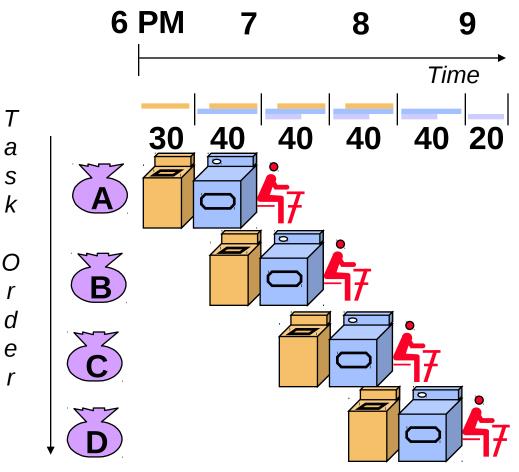

- Laundry Example

- Ann, Brian, Cathy, Dave each have one load of clothes to wash, dry, and fold

- Washer takes 30 minutes

- Dryer takes 40 minutes

- "Folder" takes 20 minutes

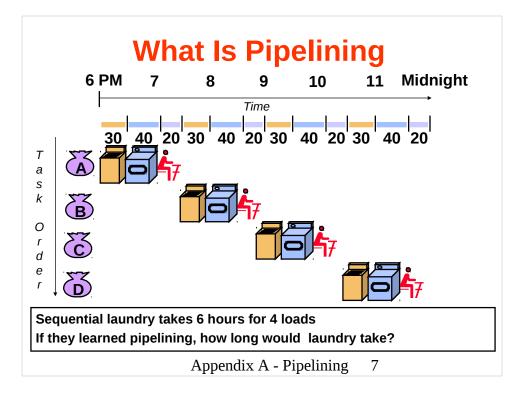

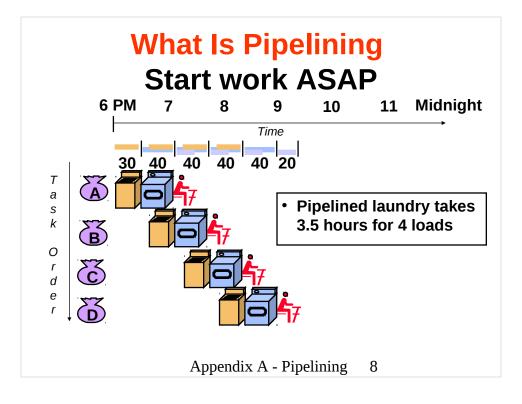

Sequential laundry takes 6 hours for 4 loads If they learned pipelining, how long would laundry take?

S

r

d

е

r

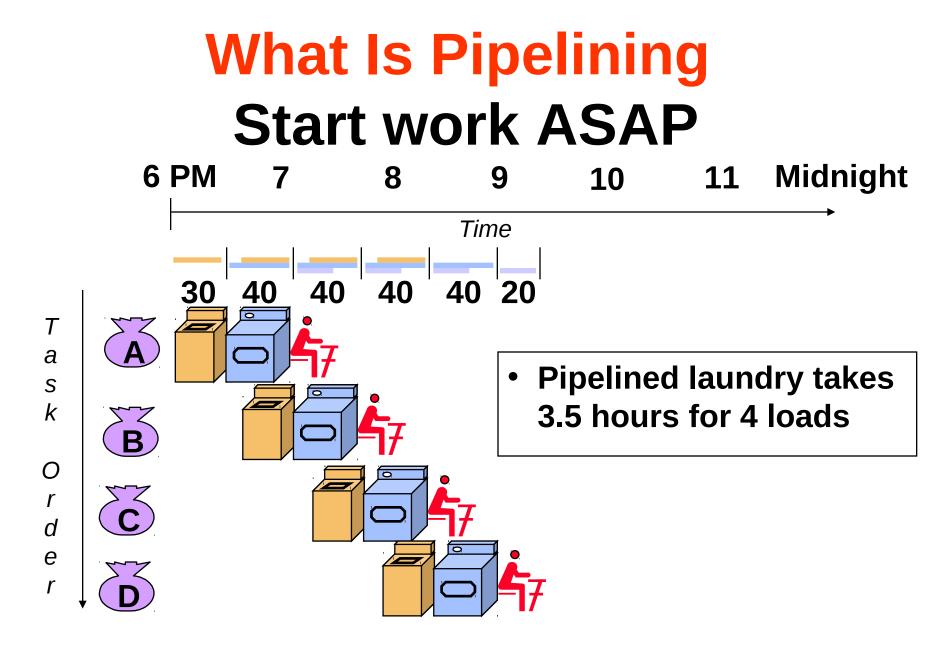

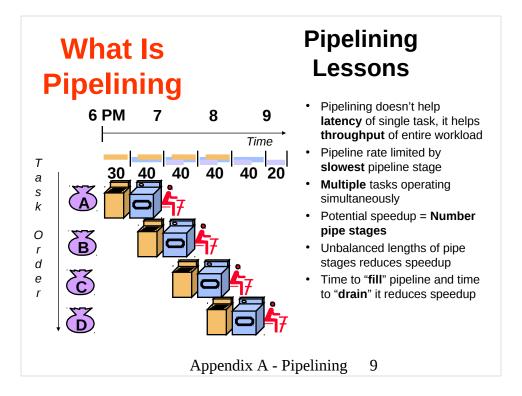

## Pipelining Lessons

- Pipelining doesn't help **latency** of single task, it helps throughput of entire workload

- Pipeline rate limited by ٠ **slowest** pipeline stage

- Multiple tasks operating • simultaneously

- Potential speedup = **Number** ٠ pipe stages

- Unbalanced lengths of pipe • stages reduces speedup

- Time to "fill" pipeline and time to "drain" it reduces speedup

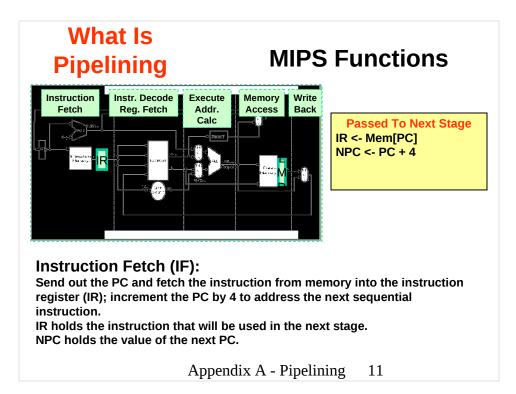

### **MIPS Functions**

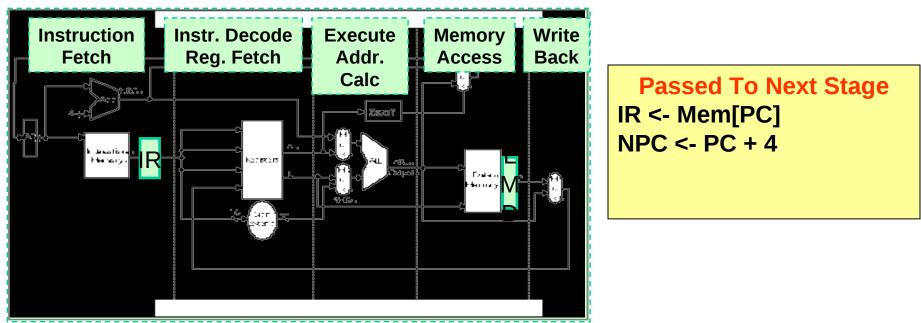

### **Instruction Fetch (IF):**

Send out the PC and fetch the instruction from memory into the instruction register (IR); increment the PC by 4 to address the next sequential instruction.

IR holds the instruction that will be used in the next stage.

NPC holds the value of the next PC.

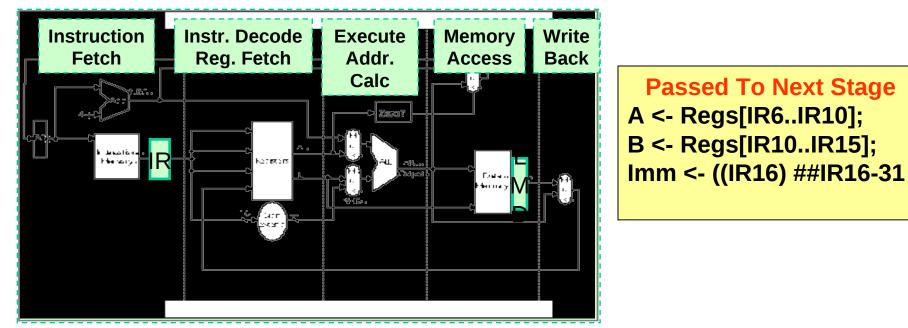

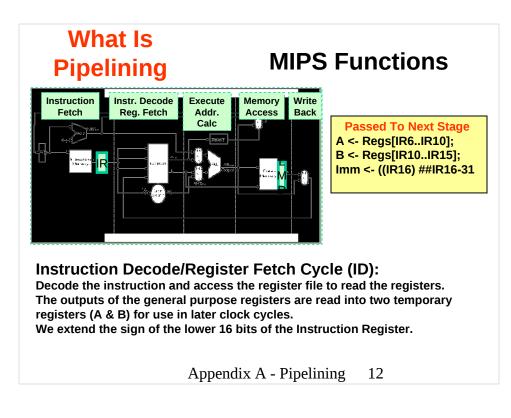

### **MIPS Functions**

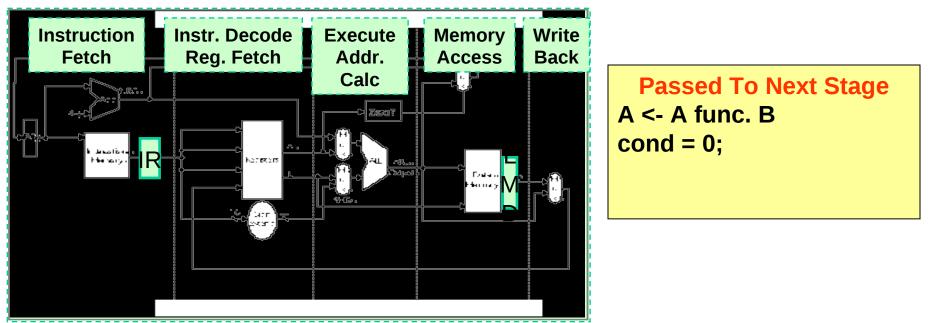

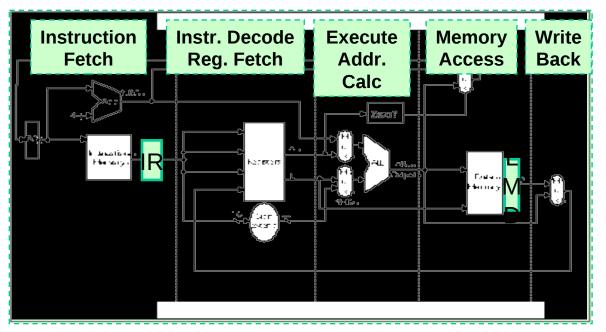

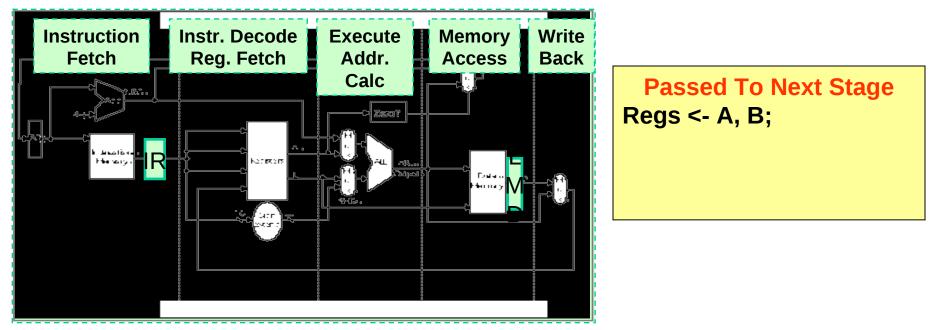

#### **Instruction Decode/Register Fetch Cycle (ID):**

Decode the instruction and access the register file to read the registers. The outputs of the general purpose registers are read into two temporary registers (A & B) for use in later clock cycles. We extend the sign of the lower 16 bits of the Instruction Register.

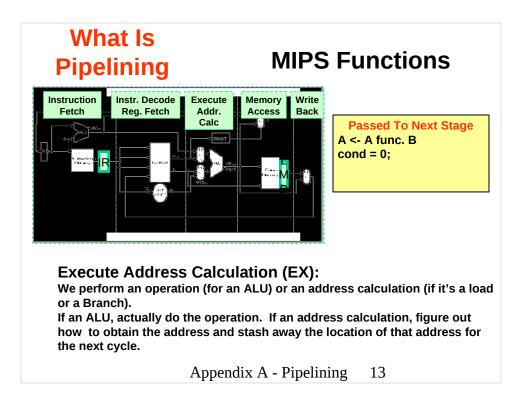

### **MIPS Functions**

#### **Execute Address Calculation (EX):**

We perform an operation (for an ALU) or an address calculation (if it's a load or a Branch).

If an ALU, actually do the operation. If an address calculation, figure out how to obtain the address and stash away the location of that address for the next cycle.

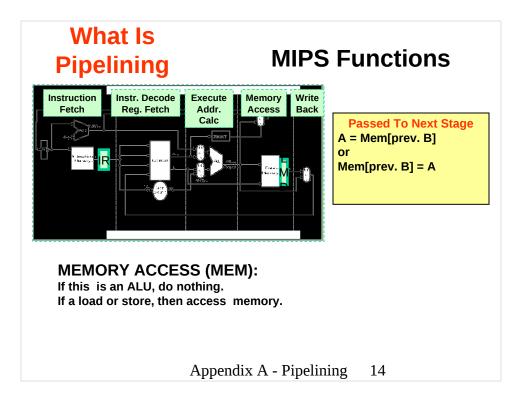

### **MIPS Functions**

Passed To Next Stage A = Mem[prev. B] or Mem[prev. B] = A

#### **MEMORY ACCESS (MEM):**

If this is an ALU, do nothing. If a load or store, then access memory.

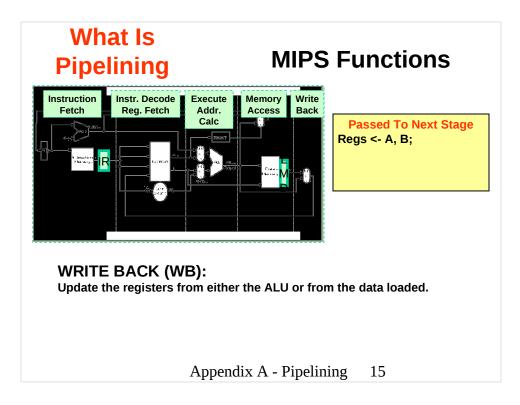

### **MIPS Functions**

#### WRITE BACK (WB):

Update the registers from either the ALU or from the data loaded.

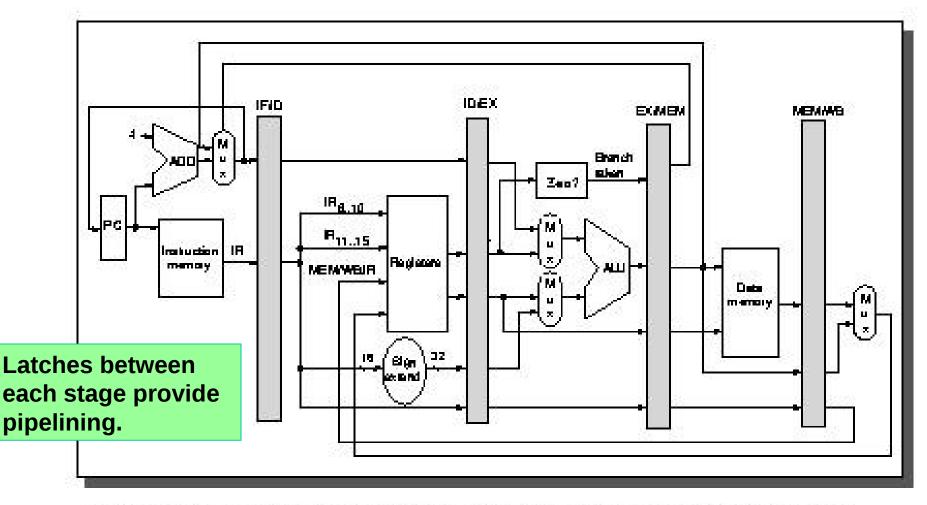

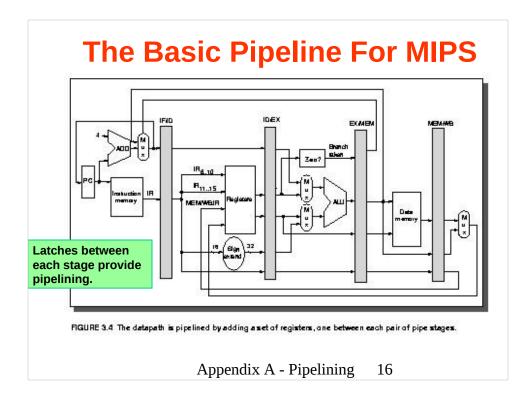

# **The Basic Pipeline For MIPS**

FIGURE 3.4 The datapath is pipelined by adding a set of registers, one between each pair of pipe stages.

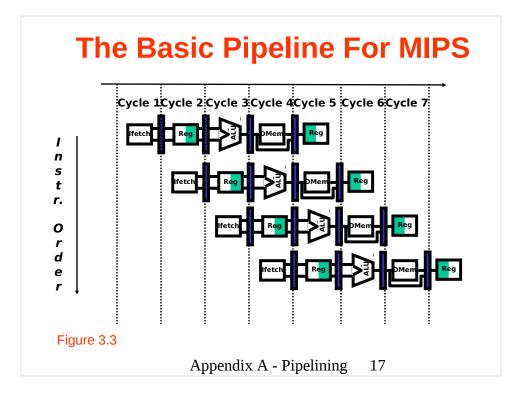

# **The Basic Pipeline For MIPS**

Figure 3.3

# **Pipeline Hurdles**

#### A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

Limits to pipelining: Hazards prevent next instruction from executing during its designated clock cycle

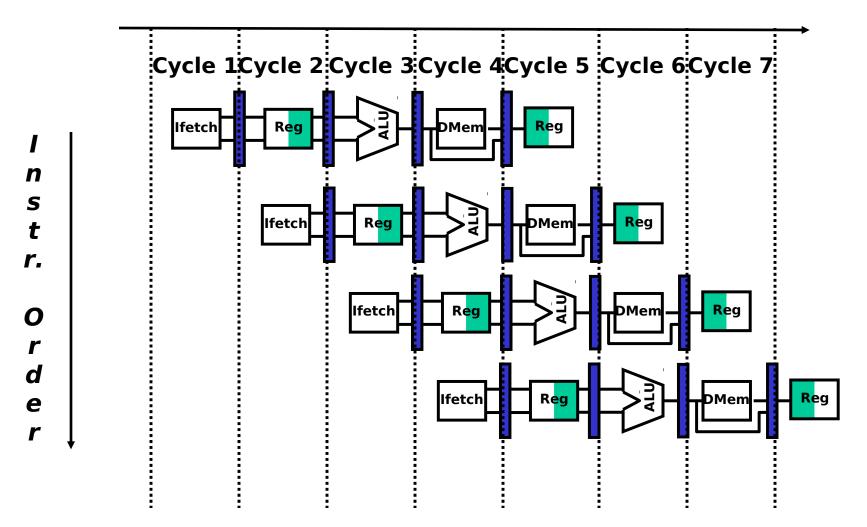

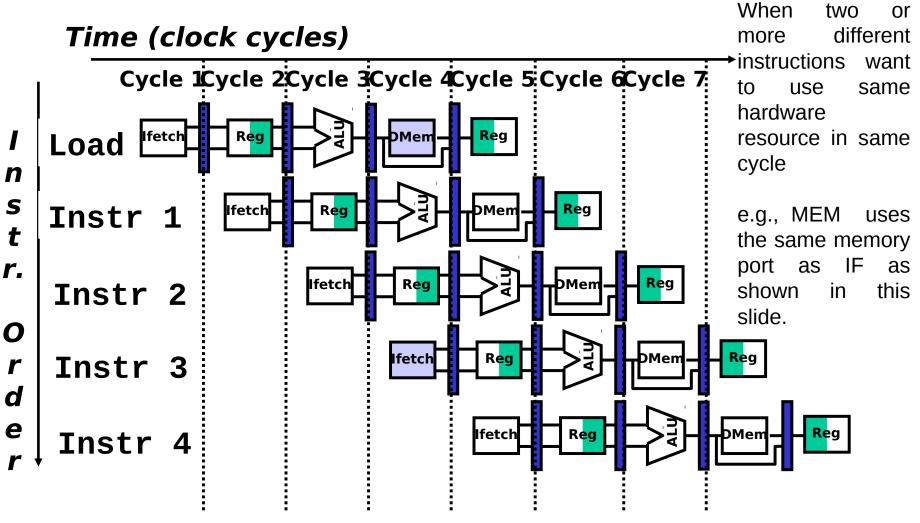

- <u>Structural hazards</u>: HW cannot support this combination of instructions (single person to fold and put clothes away)

- <u>Data hazards</u>: Instruction depends on result of prior instruction still in the pipeline (missing sock)

- <u>Control hazards</u>: Pipelining of branches & other instructions that change the PC

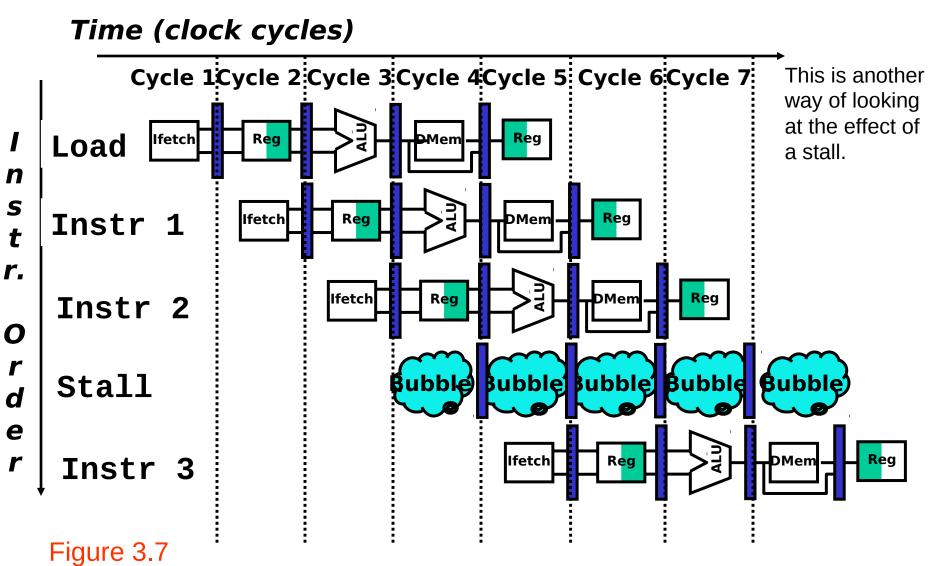

- Common solution is to <u>stall</u> the pipeline until the hazard is resolved, inserting one or more "<u>bubbles</u>" in the pipeline

# **Pipeline Hurdles**

#### Definition

- conditions that lead to incorrect behavior if not fixed

- Structural hazard

- two different instructions use same h/w in same cycle

- Data hazard

- two different instructions use same storage

- must appear as if the instructions execute in correct order

- Control hazard

- one instruction affects which instruction is next

#### Resolution

- Pipeline interlock logic detects hazards and fixes them

- simple solution: stall -

- increases CPI, decreases performance

- better solution: partial stall -

- some instruction stall, others proceed better to stall early than late

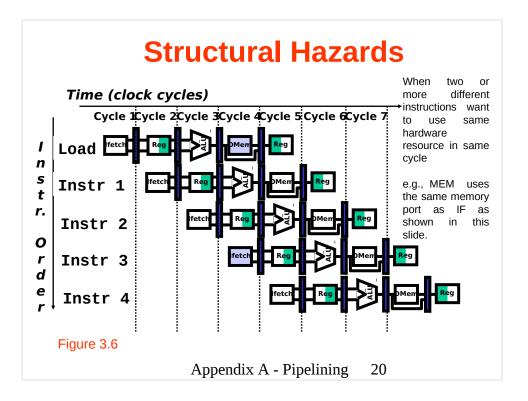

Figure 3.6

|                   |    |    |          | Clocks | yele num | ber  |    |     |     |     |

|-------------------|----|----|----------|--------|----------|------|----|-----|-----|-----|

| Instruction       | T  | 2  | 3        | 4      | 5        | 6    | 7  | 8   | 9   | 10  |

| Load instruction  | 15 | ۱D | ΕX       | MEM    | WB       |      |    |     |     |     |

| Instruction i + 1 |    | ۱F | ۱D       | EX     | MEM      | WB   |    |     |     |     |

| Instruction i + 2 |    |    | ١F       | ۱D     | ΕX       | MEM  | WB |     |     |     |

| Instruction i + 3 |    |    | 2.721.93 | stall  | 15       | ີ ເD | EΧ | MEM | WB  |     |

| Instruction i + 4 |    |    |          |        |          | ١F   | 1D | ΕX  | MEM | WB  |

| Instruction i + 5 |    |    |          |        |          |      | ١F | ۱D  | ΕX  | мем |

| lnstruction i + 6 |    |    |          |        |          |      |    | 16  | ۱D  | EX  |

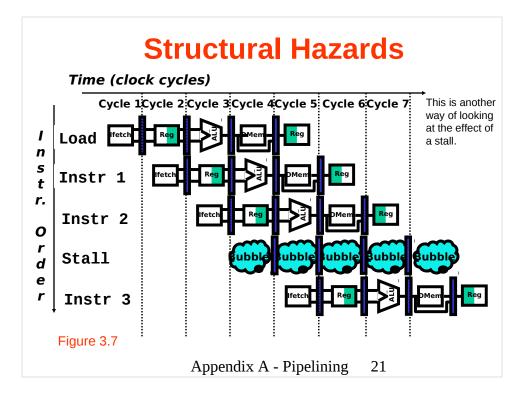

This is another way to represent the stall we saw on the last few pages.

#### **Dealing with Structural Hazards**

#### Stall

- low cost, simple

- Increases CPI

- use for rare case since stalling has performance effect

#### **Pipeline hardware resource**

- useful for multi-cycle resources

- good performance

- sometimes complex e.g., RAM

#### **Replicate resource**

- good performance

- increases cost (+ maybe interconnect delay)

- useful for cheap or divisible resources

#### **Structural hazards are reduced with these rules:**

- Each instruction uses a resource at most once

- Always use the resource in the same pipeline stage

- Use the resource for one cycle only

Many RISC ISA'a designed with this in mind

Sometimes very complex to do this. For example, memory of necessity is used in the IF and MEM stages.

#### Some common Structural Hazards:

- Memory we've already mentioned this one.

- Floating point Since many floating point instructions require many cycles, it's easy for them to interfere with each other.

- Starting up more of one type of instruction than there are resources. For instance, the PA-8600 can support two ALU + two load/store instructions per cycle that's how much hardware it has available.

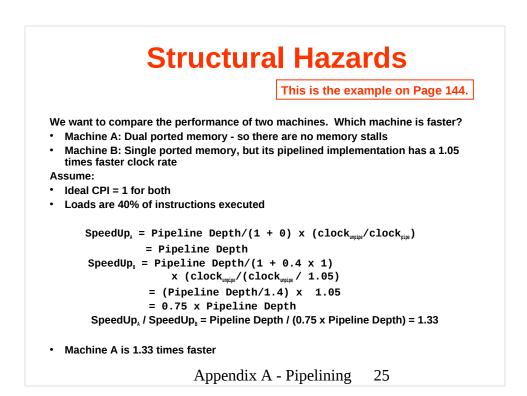

This is the example on Page 144.

We want to compare the performance of two machines. Which machine is faster?

- Machine A: Dual ported memory so there are no memory stalls

- Machine B: Single ported memory, but its pipelined implementation has a 1.05 times faster clock rate

Assume:

- Ideal CPI = 1 for both

- Loads are 40% of instructions executed

• Machine A is 1.33 times faster

- A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

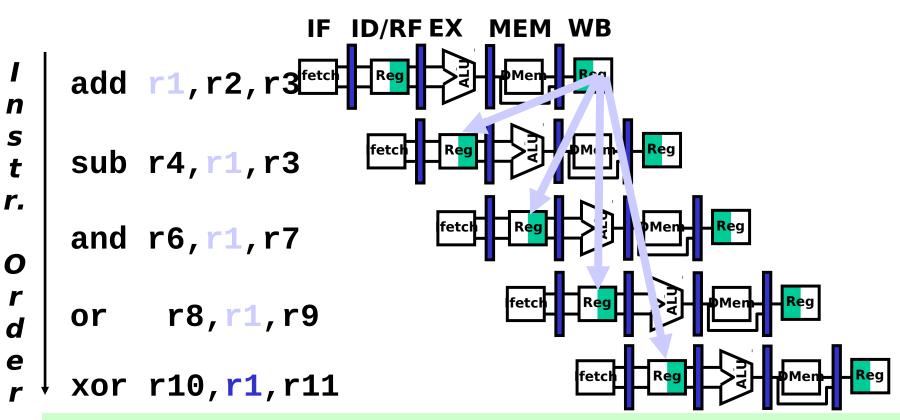

These occur when at any time, there are instructions active that need to access the same data (memory or register) locations.

Where there's real trouble is when we have:

instruction A instruction B

and B manipulates (reads or writes) data before A does. This violates the order of the instructions, since the architecture implies that A completes entirely before B is executed.

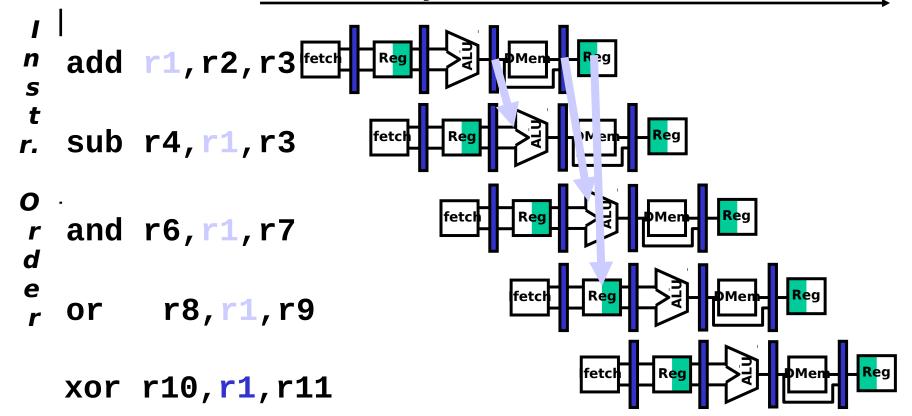

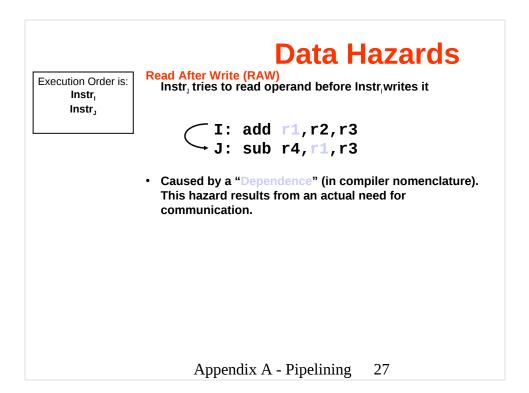

Execution Order is: Instr<sub>i</sub> Instr<sub>j</sub> **Read After Write (RAW)**

Instr, tries to read operand before Instr, writes it

|                  |     | <b>r1, r2, r3</b> |

|------------------|-----|-------------------|

| $\rightarrow$ J: | sub | r4, r1, r3        |

• Caused by a "Dependence" (in compiler nomenclature). This hazard results from an actual need for communication.

Execution Order is: Instr<sub>ı</sub> Instr<sub>ı</sub>

#### Write After Read (WAR)

Instr, tries to write operand <u>before</u> Instr, reads i

- Gets wrong operand

| ✓ I:  | sub | r4, r1, r3        |

|-------|-----|-------------------|

| ∕_ J: | add | <b>r1, r2, r3</b> |

|       |     | r6,r1,r7          |

- Called an "anti-dependence" by compiler writers. This results from reuse of the name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Reads are always in stage 2, and

- Writes are always in stage 5

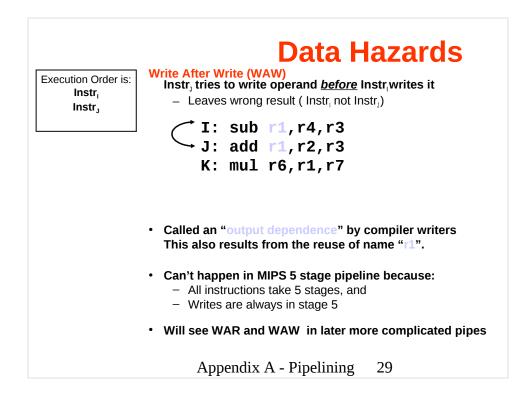

Execution Order is: Instr<sub>1</sub> Instr<sub>3</sub>

#### Write After Write (WAW)

Instr, tries to write operand *before* Instr, writes it

Leaves wrong result ( Instr, not Instr,)

| ✓ I: | sub | r1, r4, r3 |

|------|-----|------------|

| → J: | add | r1, r2, r3 |

|      |     | r6,r1,r7   |

- Called an "output dependence" by compiler writers This also results from the reuse of name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Writes are always in stage 5

- Will see WAR and WAW in later more complicated pipes

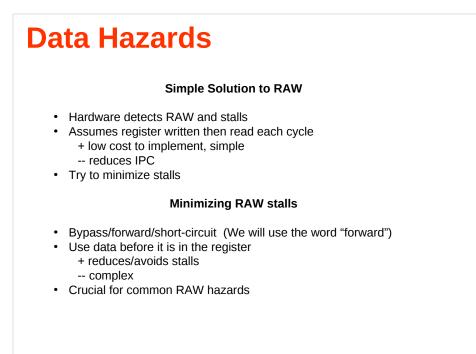

#### Simple Solution to RAW

- Hardware detects RAW and stalls

- Assumes register written then read each cycle

- + low cost to implement, simple

- -- reduces IPC

- Try to minimize stalls

#### **Minimizing RAW stalls**

- Bypass/forward/short-circuit (We will use the word "forward")

- Use data before it is in the register

- + reduces/avoids stalls

- -- complex

- Crucial for common RAW hazards

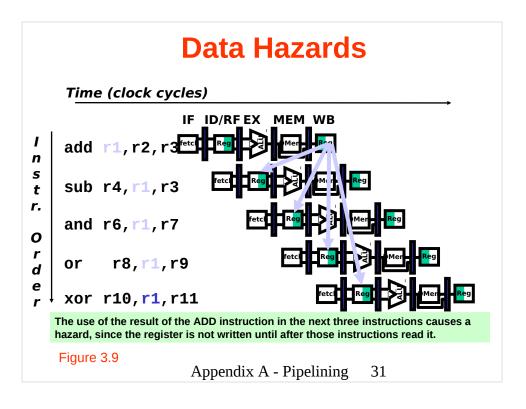

#### Time (clock cycles)

The use of the result of the ADD instruction in the next three instructions causes a hazard, since the register is not written until after those instructions read it.

#### Figure 3.9

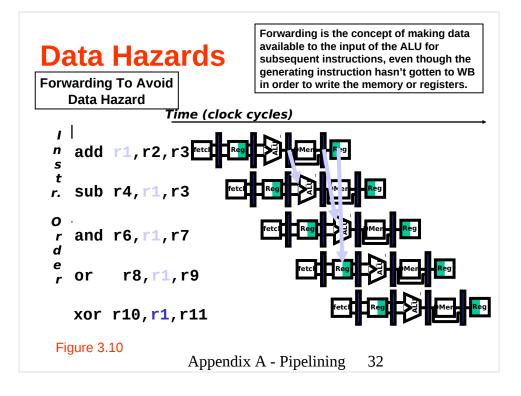

Forwarding To Avoid Data Hazard Forwarding is the concept of making data available to the input of the ALU for subsequent instructions, even though the generating instruction hasn't gotten to WB in order to write the memory or registers.

Figure 3.10

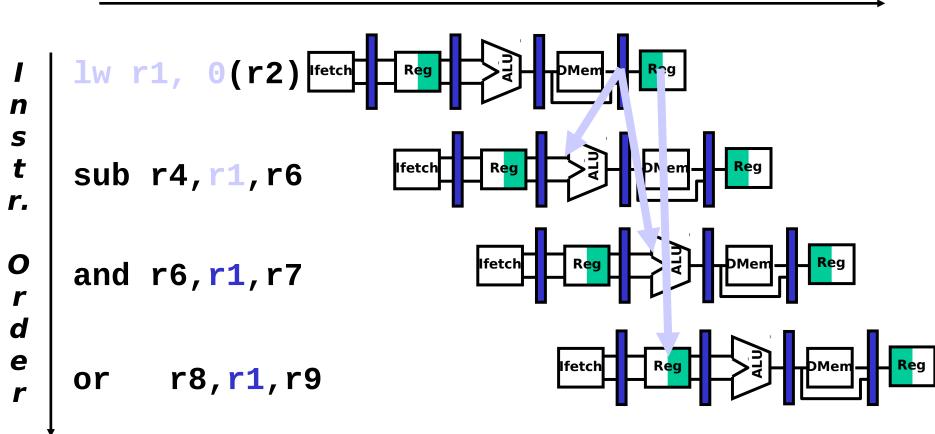

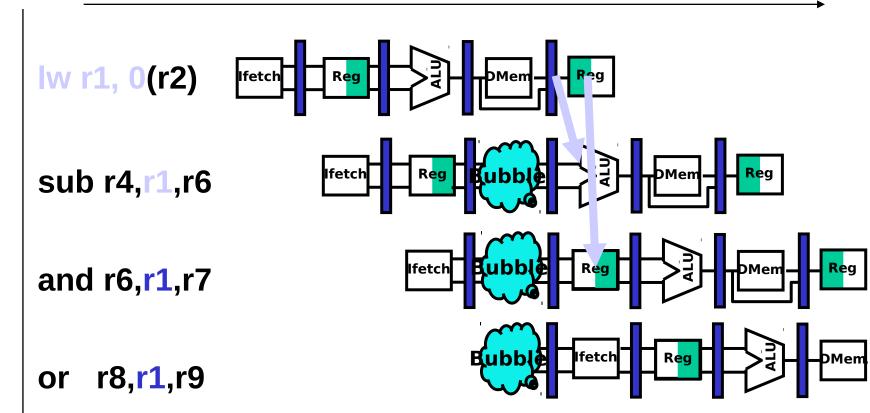

The data isn't loaded until after the MEM stage.

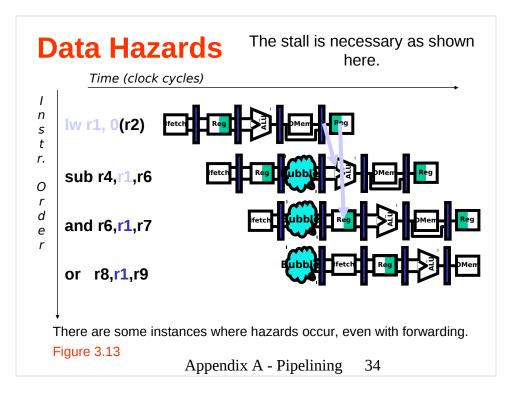

Time (clock cycles)

There are some instances where hazards occur, even with forwarding. Figure 3.12

1

n

S

t

r.

0

r

d

е

r

The stall is necessary as shown here.

There are some instances where hazards occur, even with forwarding. Figure 3.13

This is another representation of the stall.

| LW  | R1, 0(R2)  | IF | ID | EX | MEM | WB  |     |     |    |

|-----|------------|----|----|----|-----|-----|-----|-----|----|

| SUB | R4, R1, R5 |    | IF | ID | EX  | MEM | WB  |     |    |

| AND | R6, R1, R7 |    |    | IF | ID  | EX  | MEM | WB  |    |

| OR  | R8, R1, R9 |    |    |    | IF  | ID  | EX  | MEM | WB |

| LW  | R1, 0(R2)  | IF | ID | EX | MEM   | WB |     |     |     |    |  |

|-----|------------|----|----|----|-------|----|-----|-----|-----|----|--|

| SUB | R4, R1, R5 |    | IF | ID | stall | EX | MEM | WB  |     |    |  |

| AND | R6, R1, R7 |    |    | IF | stall | ID | EX  | MEM | WB  |    |  |

| OR  | R8, R1, R9 |    |    |    | stall | IF | ID  | EX  | MEM | WB |  |

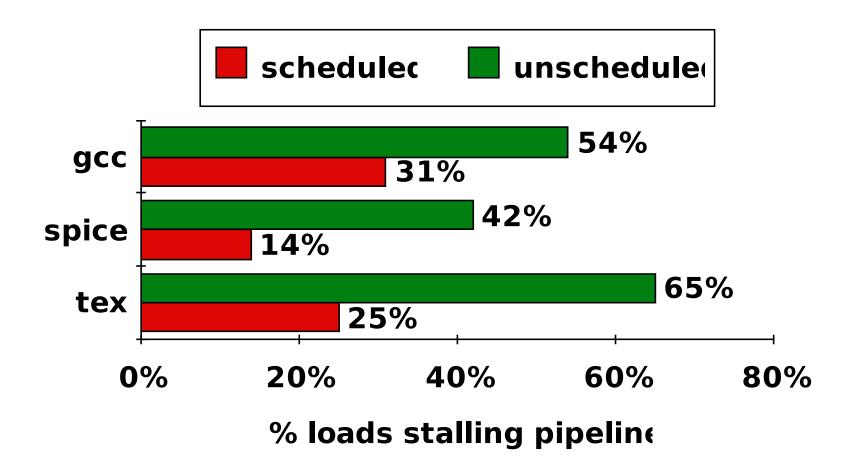

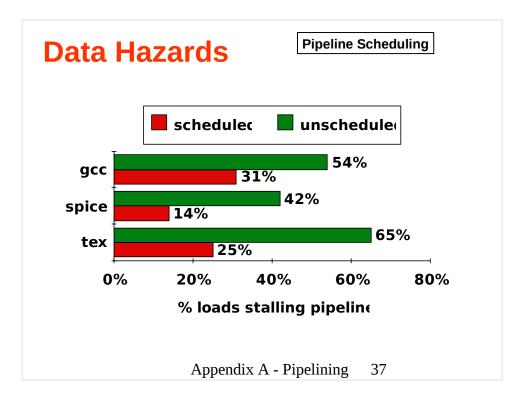

Instruction scheduled by compiler - move instruction in order to reduce stall.

| lw Rb, b       | code sequence for <b>a = b+c</b> before scheduling |

|----------------|----------------------------------------------------|

| lw Rc, c       |                                                    |

| Add Ra, Rb, Rc | stall                                              |

| sw a, Ra       |                                                    |

| lw Re, e       | code sequence for <b>d = e+f</b> before scheduling |

| lw Rf, f       |                                                    |

| sub Rd, Re, Rf | stall                                              |

| sw d, Rd       |                                                    |

Arrangement of code after scheduling.

Iw Rb, b Iw Rc, c Iw Re, e Add Ra, Rb, Rc Iw Rf, f sw a, Ra sub Rd, Re, Rf sw d, Rd

## **Data Hazards**

**Pipeline Scheduling**

- A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

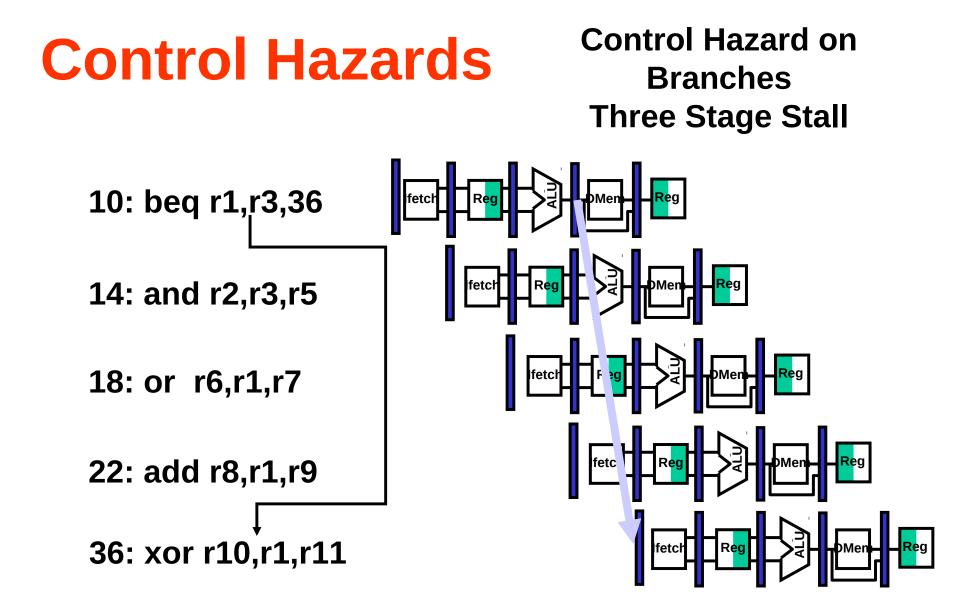

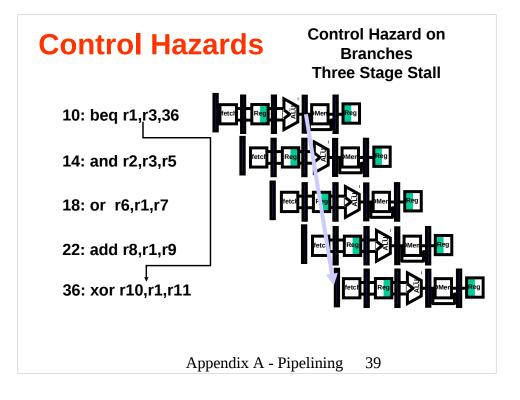

A control hazard is when we need to find the destination of a branch, and can't fetch any new instructions until we know that destination.

## **Branch Stall Impact**

- If CPI = 1, 30% branch, Stall 3 cycles => new CPI = 1.9!

- (Whoa! How did we get that 1.9???)

- Two part solution to this dramatic increase:

- Determine branch taken or not sooner, AND

- Compute taken branch address earlier

- MIPS branch tests if register = 0 or ^ 0

- MIPS Solution:

- Move Zero test to ID/RF stage

- Adder to calculate new PC in ID/RF stage

- must be fast

- can't afford to subtract

- compares with 0 are simple

- Greater-than, Less-than test sign-bit, but not-equal must OR all bits

- more general compares need ALU

- 1 clock cycle penalty for branch versus 3

In the next chapter, we'll look at ways to avoid the branch all together.

## Five Branch Hazard Alternatives

#### **#1: Stall until branch direction is clear**

### **#2: Predict Branch Not Taken**

- Execute successor instructions in sequence

- "Squash" instructions in pipeline if branch actually taken

- Advantage of late pipeline state update

- 47% MIPS branches not taken on average

- PC+4 already calculated, so use it to get next instruction

#### **#3: Predict Branch Taken**

- 53% MIPS branches taken on average

- But haven't calculated branch target address in MIPS

- MIPS still incurs 1 cycle branch penalty

- Other machines: branch target known before outcome

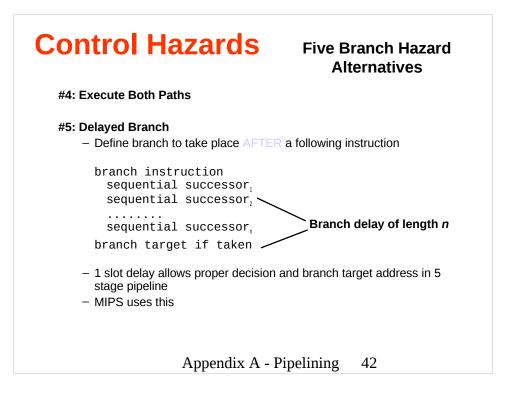

### Five Branch Hazard Alternatives

**#4: Execute Both Paths**

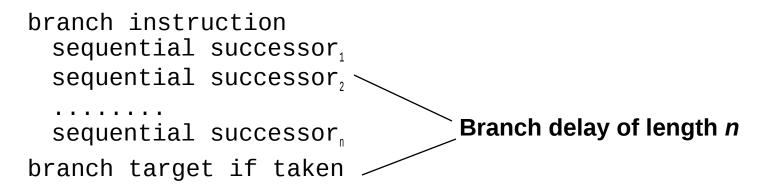

### **#5: Delayed Branch**

- Define branch to take place AFTER a following instruction

- 1 slot delay allows proper decision and branch target address in 5 stage pipeline

- MIPS uses this

## **Delayed Branch**

- Where to get instructions to fill branch delay slot?

- Before branch instruction

- From the target address: only valuable when branch taken

- From fall through: only valuable when branch not taken

- Cancelling branches allow more slots to be filled

- Compiler effectiveness for single branch delay slot:

- Fills about 60% of branch delay slots

- About 80% of instructions executed in branch delay slots useful in computation

- About 50% (60% x 80%) of slots usefully filled

- Delayed Branch downside: 7-8 stage pipelines, multiple instructions issued per clock (superscalar)

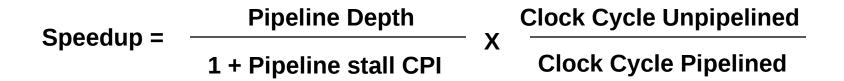

### Evaluating Branch Alternatives

Pipeline speedup =  $\frac{\text{Pipeline depth}}{1 + \text{Branch frequency} \times \text{Branch penalty}}$

| Scheduling       | Branch  | CPI  | speedup v.  | Speedup v. |  |  |

|------------------|---------|------|-------------|------------|--|--|

| scheme           | penalty |      | unpipelined | stall      |  |  |

| Stall pipeline   | 3       | 1.42 | 3.5         | 1.0        |  |  |

| Predict taken    | 1       | 1.14 | 4.4         | 1.26       |  |  |

| Predict not take | en 1    | 1.09 | 4.5         | 1.29       |  |  |

| Delayed branch   | n 0.5   | 1.07 | 4.6         | 1.31       |  |  |

**Conditional & Unconditional = 14%**,

65% change PC

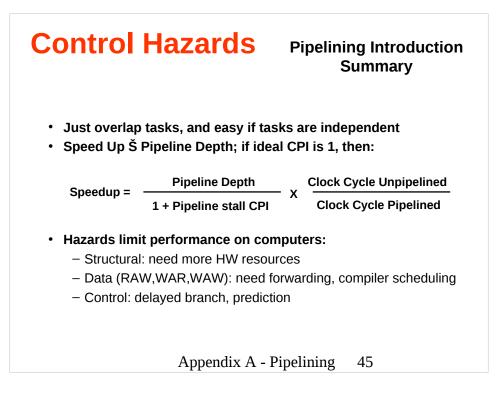

## Pipelining Introduction Summary

- Just overlap tasks, and easy if tasks are independent

- Speed Up Š Pipeline Depth; if ideal CPI is 1, then:

- Hazards limit performance on computers:

- Structural: need more HW resources

- Data (RAW,WAR,WAW): need forwarding, compiler scheduling

- Control: delayed branch, prediction

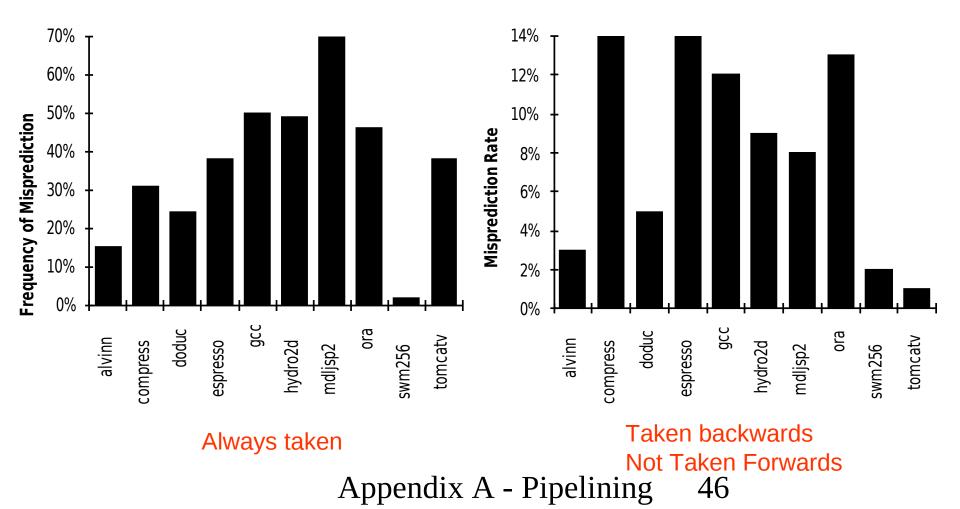

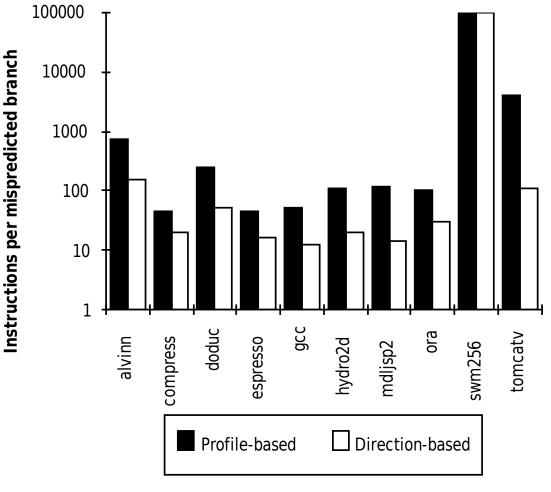

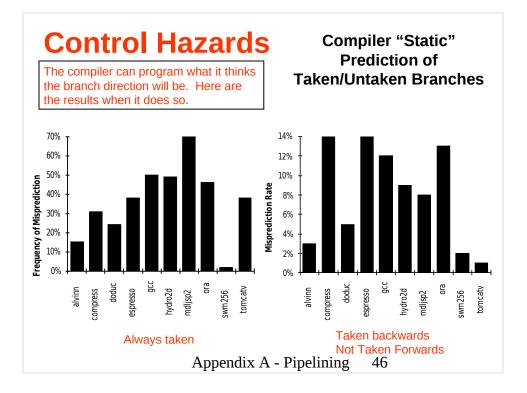

The compiler can program what it thinks the branch direction will be. Here are the results when it does so.

## Compiler "Static" Prediction of Taken/Untaken Branches

## Compiler "Static" Prediction of Taken/Untaken Branches

- Improves strategy for placing instructions in delay slot

- Two strategies

- Backward branch predict taken, forward branch not taken

- Profile-based prediction: record branch behavior, predict branch based on prior run

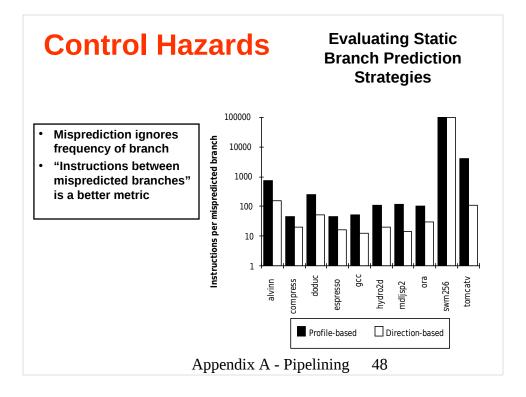

## Evaluating Static Branch Prediction Strategies

Misprediction ignores frequency of branch

"Instructions between mispredicted branches" is a better metric

#### A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

Interrupts cause great havoc!

#### **Examples of interrupts:**

- Power failing,

- Arithmetic overflow,

- I/O device request,

- OS call,

- Page fault

#### Interrupts (also known as: faults, exceptions, traps) often require

- surprise jump (to vectored address)

- linking return address

- saving of PSW (including CCs)

- state change (e.g., to kernel mode)

#### There are 5 instructions executing in 5 stage pipeline when an interrupt occurs:

- How to stop the pipeline?

- How to restart the pipeline?

- Who caused the interrupt?

### Interrupts cause great havoc!

What happens on interrupt while in delay slot ?

- Next instruction is not sequential solution #1: save multiple PCs

- Save current and next PC

- Special return sequence, more complex hardware solution #2: single PC plus

- Branch delay bit

- PC points to branch instruction

| Stage | Problem that causes the interrupt                                                         |

|-------|-------------------------------------------------------------------------------------------|

| IF    | Page fault on instruction fetch; misaligned memory<br>access; memory-protection violation |

| ID    | Undefined or illegal opcode                                                               |

| EX    | Arithmetic interrupt                                                                      |

| MEM   | Page fault on data fetch; misaligned memory<br>access; memory-protection violation        |

Interrupts cause great havoc!

- Simultaneous exceptions in more than one pipeline stage, e.g.,

- Load with data page fault in MEM stage

- Add with instruction page fault in IF stage

- Add fault will happen BEFORE load fault

- Solution #1

- Interrupt status vector per instruction

- Defer check until last stage, kill state update if exception

- Solution #2

- Interrupt ASAP

- Restart everything that is incomplete

- Another advantage for state update late in pipeline!

Interrupts cause great havoc!

| Here's what happens on a data page fault. |     |       |       |       |   |     |       |       |      |       |       |

|-------------------------------------------|-----|-------|-------|-------|---|-----|-------|-------|------|-------|-------|

|                                           | 1   | 2     | 3     | 4     | 5 | 6   | 7     | 8     | 9    |       |       |

| i                                         | F   | D     | Χ     | Μ     | W |     |       |       |      |       |       |

| i+1                                       |     | F     | D     | Χ     | Μ | W < | <- pa | age f | ault |       |       |

| i+2                                       |     |       | F     | D     | Χ | Μ   | W <   | <- sq | uash |       |       |

| i+3                                       |     |       |       | F     | D | Χ   | Μ     | W     | <- s | quasl | h     |

| i+4                                       |     |       |       |       | F | D   | Χ     | Μ     | W <  | <- si | quash |

| i+5                                       | tra | ap -> | >     |       |   | F   | D     | Χ     | Μ    | W     |       |

| i+6                                       | tra | ap ha | andle | er -> | > |     | F     | D     | Χ    | Μ     | W     |

|                                           |     |       |       |       |   |     |       |       |      |       |       |

### Complex Instructions

**Complex Addressing Modes and Instructions**

- Address modes: Autoincrement causes register change during instruction execution

- Interrupts? Need to restore register state

- Adds WAR and WAW hazards since writes are no longer the last stage.

- Memory-Memory Move Instructions

- Must be able to handle multiple page faults

- Long-lived instructions: partial state save on interrupt

- Condition Codes

# **Handling Multi-cycle Operations**

#### A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

Multi-cycle instructions also lead to pipeline complexity.

A very lengthy instruction causes everything else in the pipeline to wait for it.

## **Floating Point**

# Multi-Cycle Operations

Floating point gives long execution time.

This causes a stall of the pipeline.

It's possible to pipeline the FP execution unit so it can initiate new instructions without waiting full latency. Can also have multiple FP units.

| FP Instruction | Latency | Initiation Rate |

|----------------|---------|-----------------|

| Add, Subtract  | 4       | 3               |

| Multiply       | 8       | 4               |

| Divide         | 36      | 35              |

| Square root    | 112     | 111             |

| Negate         | 2       | 1               |

| Absolute value | 2       | 1               |

| FP compare     | 3       | 2               |

# Multi-Cycle Operations

## **Floating Point**

Divide, Square Root take -10X to -30X longer than Add

- Interrupts?

- Adds WAR and WAW hazards since pipelines are no longer same length

| i     | 1<br>IF | 2<br>ID | 3<br>EX | 4<br>MEM | 5<br>WB | 6   | 7  | 8   | 9  | 10  | 11 |

|-------|---------|---------|---------|----------|---------|-----|----|-----|----|-----|----|

| +1    |         | IF      | ID      | EX       | EX      | EX  | EX | MEM | WB |     |    |

| l + 2 |         |         | IF      | ID       | EX      | MEM | WB |     |    |     |    |

| l + 3 |         |         |         | IF       | ID      | EX  | EX | EX  | EX | MEM | WB |

| I + 4 |         |         |         |          | IF      | ID  | EX | MEM | WB |     |    |

| l + 5 |         |         |         |          |         | IF  | ID |     |    | EX  | EX |

| l + 6 |         |         |         |          |         |     | IF |     |    | ID  | EX |

**Notes:**

- I + 2: no WAW, but this complicates an interrupt

- I + 4: no WB conflict

- I + 5: stall forced by structural hazard

- I + 6: stall forced by in-order issue

# **Summary of Pipelining Basics**

- Hazards limit performance

- Structural: need more HW resources

- Data: need forwarding, compiler scheduling

- Control: early evaluation & PC, delayed branch, prediction

- Increasing length of pipe increases impact of hazards; pipelining helps instruction bandwidth, not latency

- Interrupts, Instruction Set, FP makes pipelining harder

- Compilers reduce cost of data and control hazards

- Load delay slots

- Branch delay slots

- Branch prediction

## **Credits**

I have not written these notes by myself. There's a great deal of fancy artwork here that takes considerable time to prepare.

I have borrowed from:

Wen-mei & Patel: http://courses.ece.uiuc.edu/ece511/lectures/lecture3.ppt

Patterson: http://www.cs.berkeley.edu/~pattrsn/252S98/index.html

Rabaey: (He used lots of Patterson material):

http://bwrc.eecs.berkeley.edu/Classes/CS252/index.htm

Katz: (Again, he borrowed heavily from Patterson):

http://http.cs.berkeley.edu/~randy/Courses/CS252.F95/CS252.Intro.html

Mark Hill: (Follows text fairly well): http://www.cs.wisc.edu/~markhill/cs752/

#### A.1 What is Pipelining?

A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

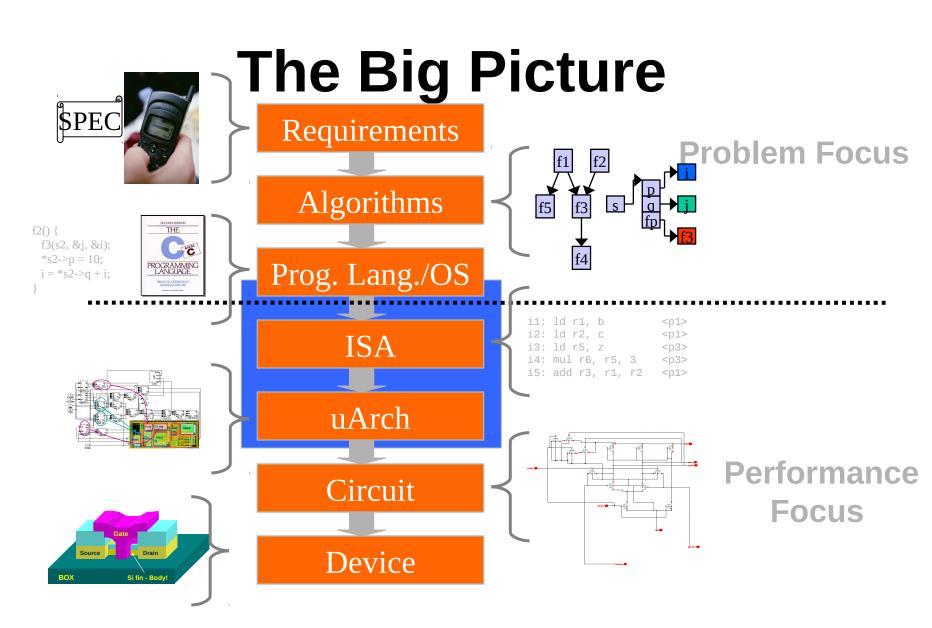

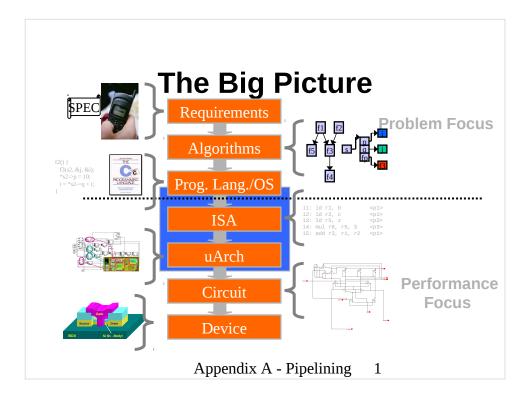

The big picture. Talk about the levels of abstraction. Talk about the fact that this is where all programs get ushered into hardware execution.

Circuits are increasing providing both opportunities (resources, bandwidth) and challenges (noise, power).

Circuits are locally designed; software is globally intertwined

Software is increasingly over designed for portability and productivity.

The path between the two domains is increasingly stressed and inadequate due to this mismatch.

The focus of the thrust is to provide a very strong path from the productivity oriented software domain into the performance oriented hardware domain.

Translate device/circuit level innovations into visible benefit at the application/software level!

### **Traditional Issues**

- Strongly constrained by the number of bits available to instruction encoding

- Opcodes/operands

- Registers/memory

- Addressing modes

- Orthogonality

- 0, 1, 2, 3 address machines

- Instruction formats

- Decoding uniformity

### Introduction

A.1 What is Pipelining?

A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

## **Pipeline Hurdles**

#### A.1 What is Pipelining?

- A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

- Limits to pipelining: Hazards prevent next instruction from executing during its designated clock cycle

- <u>Structural hazards</u>: HW cannot support this combination of instructions (single person to fold and put clothes away)

- <u>Data hazards</u>: Instruction depends on result of prior instruction still in the pipeline (missing sock)

- <u>Control hazards</u>: Pipelining of branches & other instructions that change the PC

- Common solution is to <u>stall</u> the pipeline until the hazard is resolved, inserting one or more "<u>bubbles</u>" in the pipeline

# **Pipeline Hurdles**

#### Definition

- · conditions that lead to incorrect behavior if not fixed

- Structural hazard

- two different instructions use same h/w in same cycle

- Data hazard

- two different instructions use same storage

- must appear as if the instructions execute in correct order

- Control hazard

- one instruction affects which instruction is next

#### Resolution

- · Pipeline interlock logic detects hazards and fixes them

- simple solution: stall -

- increases CPI, decreases performance

- · better solution: partial stall -

- · some instruction stall, others proceed better to stall early than late

# **Structural Hazards**

|                   | Clock cycle number |    |    |       |     |     |    |     |     |     |

|-------------------|--------------------|----|----|-------|-----|-----|----|-----|-----|-----|

| Instruction       | T                  | 2  | 3  | 4     | 5   | 6   | 7  | 8   | 9   | 10  |

| Load instruction  | ۱F                 | ۱D | EX | MEM   | WB  |     |    |     |     |     |

| Instruction i + 1 |                    | ۱F | ۱D | EΧ    | MEM | WB  |    |     |     |     |

| Instruction i + 2 |                    |    | ۱F | ۱D    | ΕX  | MEM | WB |     |     |     |

| Instruction i + 3 |                    |    |    | stall | 1F  | lD  | EX | MEM | WB  |     |

| Instruction i + 4 |                    |    |    |       |     | ۱F  | ۱D | БX  | MEM | WB  |

| Instruction i + 5 |                    |    |    |       |     |     | ۱F | ۱D  | EX  | MEM |

| Instruction i + 6 |                    |    |    |       |     |     |    | ١F  | ۱D  | EX  |

This is another way to represent the stall we saw on the last few pages.

# **Structural Hazards**

### **Dealing with Structural Hazards**

### Stall

- · low cost, simple

- Increases CPI

- use for rare case since stalling has performance effect

### Pipeline hardware resource

- useful for multi-cycle resources

- good performance

- sometimes complex e.g., RAM

### **Replicate resource**

- good performance

- increases cost (+ maybe interconnect delay)

- useful for cheap or divisible resources

# **Structural Hazards**

Structural hazards are reduced with these rules:

- Each instruction uses a resource at most once

- · Always use the resource in the same pipeline stage

- · Use the resource for one cycle only

Many RISC ISA'a designed with this in mind

Sometimes very complex to do this. For example, memory of necessity is used in the IF and MEM stages.

### Some common Structural Hazards:

- Memory we've already mentioned this one.

- Floating point Since many floating point instructions require many cycles, it's easy for them to interfere with each other.

- Starting up more of one type of instruction than there are resources. For instance, the PA-8600 can support two ALU + two load/store instructions per cycle that's how much hardware it has available.

#### A.1 What is Pipelining?

#### A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

A.3 How is Pipelining Implemented

A.4 What Makes Pipelining Hard to Implement?

A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

## **Data Hazards**

These occur when at any time, there are instructions active that need to access the same data (memory or register) locations.

Where there's real trouble is when we have:

instruction A instruction B

and B manipulates (reads or writes) data before A does. This violates the order of the instructions, since the architecture implies that A completes entirely before B is executed.

| Execution Order is:<br>Instr,<br>Instr <sub>3</sub> | Data Hazards<br>Write After Read (WAR)<br>Instr, tries to write operand <u>before</u> Instr, reads i<br>– Gets wrong operand<br>I: sub r4, r1, r3<br>J: add r1, r2, r3     |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | K: mul r6,r1,r7                                                                                                                                                            |

|                                                     | <ul> <li>Called an "anti-dependence" by compiler writers.<br/>This results from reuse of the name "r1".</li> <li>Can't happen in MIPS 5 stage pipeline because:</li> </ul> |

|                                                     | <ul> <li>All instructions take 5 stages, and</li> <li>Reads are always in stage 2, and</li> <li>Writes are always in stage 5</li> </ul>                                    |

|                                                     | Appendix A - Pipelining 28                                                                                                                                                 |

| Data Hazards This is another representation of the stall. |                            |    |    |    |      |      |      |       |      |    |

|-----------------------------------------------------------|----------------------------|----|----|----|------|------|------|-------|------|----|

| LW                                                        | R1, 0(R2)                  | IF |    | ID | EX   | MEM  | WB   |       |      |    |

| SUB                                                       | R4, R1, R5                 |    |    | IF | ID   | EX   | MEM  | WB    |      |    |

| AND                                                       | R6, R1, R7                 |    |    |    | IF   | ID   | EX   | MEM   | WB   |    |

| OR                                                        | R8, R1, R9                 |    |    |    |      | IF   | ID   | EX    | MEM  | WB |

| LW                                                        | R1, 0(R2)                  | IF | ID | EX | MEN  | лw   | В    |       |      |    |

| SUB                                                       | R4, R1, R5                 |    | IF | ID | stal | ΙE   | х ме | M WE  | 3    |    |

| AND                                                       | R6, R1, R7                 |    |    | IF | stal | 1 11 | D EX | K MEI | M WB |    |

| OR                                                        | R8, R1, R9                 |    |    |    | stal | I II | = 10 | ) EX  | MEM  | WB |

|                                                           | Appendix A - Pipelining 35 |    |    |    |      |      |      |       |      |    |

## **Data Hazards**

**Pipeline Scheduling**

Instruction scheduled by compiler - move instruction in order to reduce stall.

Iw Rb, b-- code sequence for a = b+c before schedulingIw Rc, c-- stallAdd Ra, Rb, Rc-- stallsw a, Ra-- code sequence for d = e+f before schedulingIw Re, e-- code sequence for d = e+f before schedulingIw Rf, f-- stallsub Rd, Re, Rf-- stallsw d, Rd-- stall

Arrangement of code after scheduling.

Iw Rb, b Iw Rc, c Iw Re, e Add Ra, Rb, Rc Iw Rf, f sw a, Ra sub Rd, Re, Rf sw d, Rd

A.1 What is Pipelining?

A.2 The Major Hurdle of Pipelining-Structural Hazards

- -- Structural Hazards

- Data Hazards

- Control Hazards

A.3 How is Pipelining Implemented

- A.4 What Makes Pipelining Hard to Implement?

- A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations

A control hazard is when we need to find the destination of a branch, and can't fetch any new instructions until we know that destination.

## **Branch Stall Impact**

- If CPI = 1, 30% branch, Stall 3 cycles => new CPI = 1.9!

- (Whoa! How did we get that 1.9???)

- Two part solution to this dramatic increase:

- Determine branch taken or not sooner, AND

- Compute taken branch address earlier

- MIPS branch tests if register = 0 or ^ 0

### • MIPS Solution:

- Move Zero test to ID/RF stage

- Adder to calculate new PC in ID/RF stage

- must be fast

- · can't afford to subtract

- compares with 0 are simple

- · Greater-than, Less-than test sign-bit, but not-equal must OR all bits

- more general compares need ALU

- 1 clock cycle penalty for branch versus 3

In the next chapter, we'll look at ways to avoid the branch all together.

### Five Branch Hazard Alternatives

### #1: Stall until branch direction is clear

### #2: Predict Branch Not Taken

- Execute successor instructions in sequence

- "Squash" instructions in pipeline if branch actually taken

- Advantage of late pipeline state update

- 47% MIPS branches not taken on average

- PC+4 already calculated, so use it to get next instruction

### #3: Predict Branch Taken

- 53% MIPS branches taken on average

- But haven't calculated branch target address in MIPS

- MIPS still incurs 1 cycle branch penalty

- Other machines: branch target known before outcome

### Evaluating Branch Alternatives

Pipeline speedup =  $\frac{\text{Pipeline depth}}{1 + \text{Branch frequency} \times \text{Branch penalty}}$

|                                                  | ranch<br>enalty | CPI  | speedup v.<br>unpipelined | Speedup v.<br>stall |  |  |  |  |

|--------------------------------------------------|-----------------|------|---------------------------|---------------------|--|--|--|--|

| Stall pipeline                                   | 3               | 1.42 | 3.5                       | 1.0                 |  |  |  |  |

| Predict taken                                    | 1               | 1.14 | 4.4                       | 1.26                |  |  |  |  |

| Predict not taken                                | 1 <b>1</b>      | 1.09 | 4.5                       | 1.29                |  |  |  |  |

| Delayed branch                                   | 0.5             | 1.07 | 4.6                       | 1.31                |  |  |  |  |

| Conditional & Unconditional = 14%, 65% change PC |                 |      |                           |                     |  |  |  |  |

Compiler "Static" Prediction of Taken/Untaken Branches

• Improves strategy for placing instructions in delay slot

### • Two strategies

- Backward branch predict taken, forward branch not taken

- Profile-based prediction: record branch behavior, predict branch based on prior run

# <section-header> A. Mata Bripelining A. A Mata September Septemb

#### Interrupts cause great havoc!

#### **Examples of interrupts:**

- Power failing,

- · Arithmetic overflow,

- I/O device request,

- OS call,

- Page fault

#### Interrupts (also known as: faults, exceptions, traps) often require

- surprise jump (to vectored address)

- linking return address

- saving of PSW (including CCs)

- state change (e.g., to kernel mode)

#### There are 5 instructions executing in 5 stage pipeline when an interrupt occurs:

- How to stop the pipeline?

- How to restart the pipeline?

- Who caused the interrupt?

## Interrupts cause great havoc!

What happens on interrupt while in delay slot ?

- Next instruction is not sequential

- solution #1: save multiple PCs

- Save current and next PC

- Special return sequence, more complex hardware solution #2: single PC plus

- Branch delay bit

- PC points to branch instruction

| Stage | Problem that causes the interrupt                                                         |

|-------|-------------------------------------------------------------------------------------------|

| IF    | Page fault on instruction fetch; misaligned memory<br>access; memory-protection violation |

| ID    | Undefined or illegal opcode                                                               |

| EX    | Arithmetic interrupt                                                                      |

| MEM   | Page fault on data fetch; misaligned memory<br>access; memory-protection violation        |

|       | Appendix A - Pipelining 51                                                                |

Interrupts cause great havoc!

- · Simultaneous exceptions in more than one pipeline stage, e.g.,

- Load with data page fault in MEM stage

- Add with instruction page fault in IF stage

- Add fault will happen BEFORE load fault

- Solution #1

- Interrupt status vector per instruction

- Defer check until last stage, kill state update if exception

- Solution #2

- Interrupt ASAP

- Restart everything that is incomplete

Another advantage for state update late in pipeline!

Interrupts cause great havoc!

|     | 1   | 2     | 3     | 4     | 5 | 6 | 7     | 8     | 9    |       |       |

|-----|-----|-------|-------|-------|---|---|-------|-------|------|-------|-------|

| i   | F   | D     | Х     | М     | W |   |       |       |      |       |       |

| i+1 |     | F     | D     | Х     | М | W | <- pa | age f | ault |       |       |

| i+2 |     |       | F     | D     | Х | М | W <   | <- sq | uash |       |       |

| i+3 |     |       |       | F     | D | Х | М     | W     | <- s | quasł | า     |

| i+4 |     |       |       |       | F | D | Х     | М     | W    | <- so | quash |

| i+5 | tra | ap -> | >     |       |   | F | D     | Х     | М    | W     |       |

| i+6 | tra | ap ha | andle | er -> | > |   | F     | D     | Х    | м     | W     |

Complex Instructions

#### **Complex Addressing Modes and Instructions**

- Address modes: Autoincrement causes register change during instruction execution

- Interrupts? Need to restore register state

- Adds WAR and WAW hazards since writes are no longer the last stage.

- Memory-Memory Move Instructions

- Must be able to handle multiple page faults

- Long-lived instructions: partial state save on interrupt

- Condition Codes

# **Handling Multi-cycle Operations**

#### A.1 What is Pipelining?

#### A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

- A.3 How is Pipelining Implemented

A.4 What Makes Pipelining Hard to Implement?

A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations Multi-cycle instructions also lead to pipeline complexity.

A very lengthy instruction causes everything else in the pipeline to wait for it.

**Floating Point**

## Multi-Cycle Operations

Floating point gives long execution time.

This causes a stall of the pipeline.

It's possible to pipeline the FP execution unit so it can initiate new instructions without waiting full latency. Can also have multiple FP units.

| Latency | Initiation Rate               |

|---------|-------------------------------|

| 4       | 3                             |

| 8       | 4                             |

| 36      | 35                            |

| 112     | 111                           |

| 2       | 1                             |

| 2       | 1                             |

| 3       | 2                             |

|         | 4<br>8<br>36<br>112<br>2<br>2 |

| Multi-Cycle                                 |              |                             |                     |                                                |                     |                                  |                                       | Floa                          | oating Point                |                           |                      |  |

|---------------------------------------------|--------------|-----------------------------|---------------------|------------------------------------------------|---------------------|----------------------------------|---------------------------------------|-------------------------------|-----------------------------|---------------------------|----------------------|--|

|                                             |              |                             | Divid<br>-          | e, Squa<br>Interru<br>Adds                     | upts?<br>WAR a      |                                  | W haz                                 |                               | •                           | <b>er than</b><br>pelines |                      |  |

| i<br> +1<br> +2<br> +3<br> +4<br> +5<br> +6 | 1<br>IF      | 2<br>ID<br>IF               | 3<br>EX<br>ID<br>IF |                                                |                     | 6<br>EX<br>MEM<br>EX<br>ID<br>IF | 7<br>EX<br>WB<br>EX<br>EX<br>ID<br>IF | 8<br>MEM<br>EX<br>MEM<br><br> | 9<br>WB<br>EX<br>WB<br><br> | 10<br>MEM<br>EX<br>ID     | 11<br>WB<br>EX<br>EX |  |

|                                             | + 4<br>  + 5 | : no V<br>: no V<br>: stall | /B con<br>forced    | ut this<br>flict<br>by stru<br>by in-c<br>Appe | ictural<br>order is | l hazar<br>ssue                  | d                                     |                               | 57                          |                           |                      |  |

# **Summary of Pipelining Basics**

#### • Hazards limit performance

- Structural: need more HW resources

- Data: need forwarding, compiler scheduling

- Control: early evaluation & PC, delayed branch, prediction

- Increasing length of pipe increases impact of hazards; pipelining helps instruction bandwidth, not latency

- Interrupts, Instruction Set, FP makes pipelining harder

- Compilers reduce cost of data and control hazards

- Load delay slots

- Branch delay slots

- Branch prediction

| Credits                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------|

| I have not written these notes by myself. There's a great deal of fancy artwork here that takes considerable time to prepare. |

| I have borrowed from:                                                                                                         |

| Wen-mei & Patel: http://courses.ece.uiuc.edu/ece511/lectures/lecture3.ppt                                                     |

| Patterson: http://www.cs.berkeley.edu/~pattrsn/252S98/index.html                                                              |

| Rabaey: (He used lots of Patterson material):                                                                                 |

| http://bwrc.eecs.berkeley.edu/Classes/CS252/index.htm                                                                         |

| Katz: (Again, he borrowed heavily from Patterson):                                                                            |

| http://http.cs.berkeley.edu/~randy/Courses/CS252.F95/CS252.Intro.html                                                         |

| Mark Hill: (Follows text fairly well): http://www.cs.wisc.edu/~markhill/cs752/                                                |

#### Summary

A.1 What is Pipelining?

A.2 The Major Hurdle of Pipelining-Structural Hazards

- Data Hazards

- Control Hazards

A.3 How is Pipelining Implemented

A.4 What Makes Pipelining Hard to Implement?

A.5 Extending the MIPS Pipeline to Handle Multi-cycle Operations