|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory: cache |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

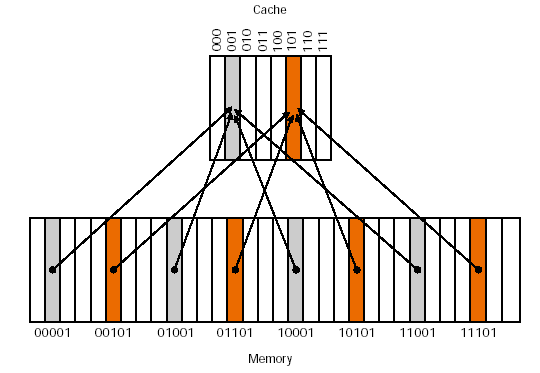

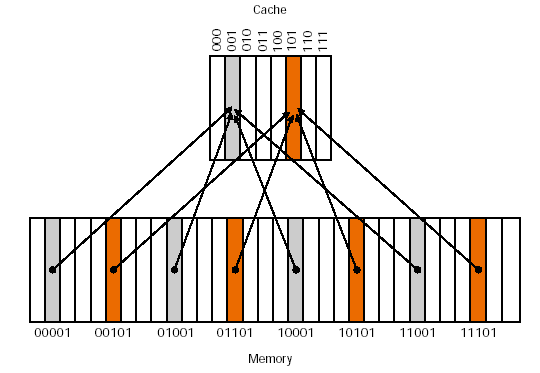

Fig 7.4 |

|

|

|

|

|

|

|

|

|

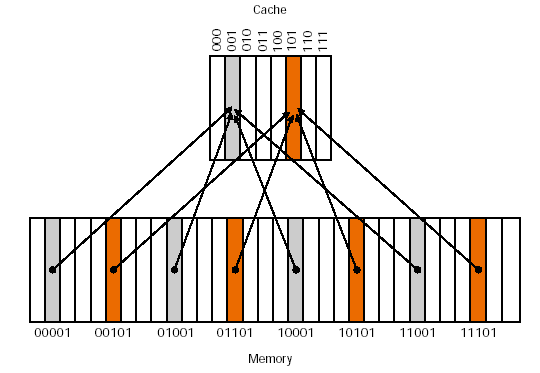

Consider simple cache |

|

|

|

|

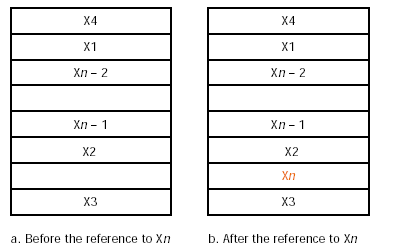

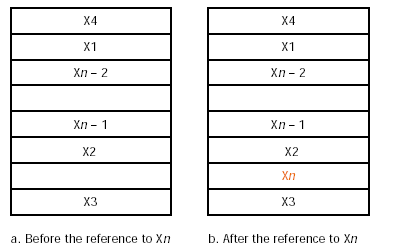

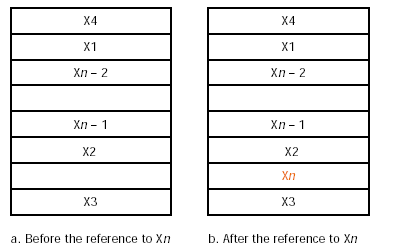

Processor requests are

each 1 word |

|

|

|

|

|

Cache blocks are 1 word |

|

|

|

Processor makes

reference to word Xn, and Xn is not currently in the cache: cache miss |

|

If there is space in the

cache, then word Xn is copied into the cache |

|

|

|

2 questions: |

|

|

|

|

|

How do we know if a data

item is in the cache now? |

|

|

|

|

If so, where is it

located? |

|

|

|

|

Simplest method: |

|

|

|

|

|

|

Base cache address

directly on memory address: direct mapped cache |

|

|

|

(Notice they are not

equal, since the cache is smaller) |

|

|

|

Typical method: |

|

|

|

|

|

|

(block address) mod

(number of cache blocks in whole

cache) |

|

|

|

Easy to compute if

number of cache blocks is power of 2: use low order n bits of address |

|

where n is log 2 (number of cache blocks) |

|

|

|

Example: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig 7.5 |

|

|

|

|

|

|

Cache of 8 words |

|

|

|

|

Each data word is mapped

to location whose address ends in same 3 bits |

|

|

For example, all the

gray words have addresses ending in 001, |

|

|

|

mapped to cache block 001 |

|

|

|

Each cache location can

contain several possible data words |

|

|

|

|

If a word is in the

cache, how do we know which one it is? |

|

|

|

Add tags to the cache

entries |

|

|

|

|

Tag

needs to contain only the upper bits of the address |

|

|

|

In example, only need

upper 2 bits for tag |

|

|

|

Also need to recognize

whether block is empty: valid bit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|