|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Multi-cycle control:

microprogram |

|

|

|

|

|

|

|

Disadvantages of FSM |

|

|

|

Very complex for 100

instructions, even with MIPS architecture |

|

|

|

Instructions take 1-20

clock cycles |

|

|

|

Large number of states:

100s or more |

|

|

|

Microprogram: another level of abstraction, simplifies control design |

|

|

|

|

Each microinstruction

specifies the set of control signals in a given state |

|

|

Executing a

microinstruction: assert the specified control signals |

|

|

|

Sequencing: |

|

|

|

|

|

Unconditional: go to

single next state |

|

|

|

Conditional: next state

depends on input |

|

|

|

|

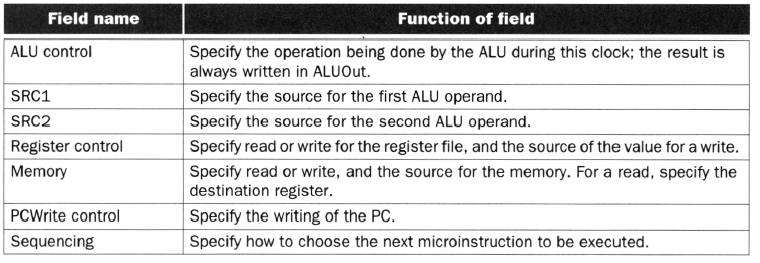

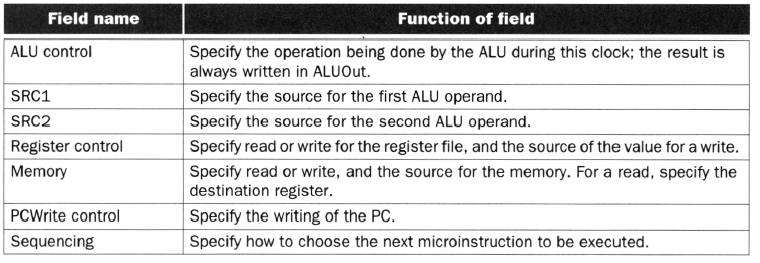

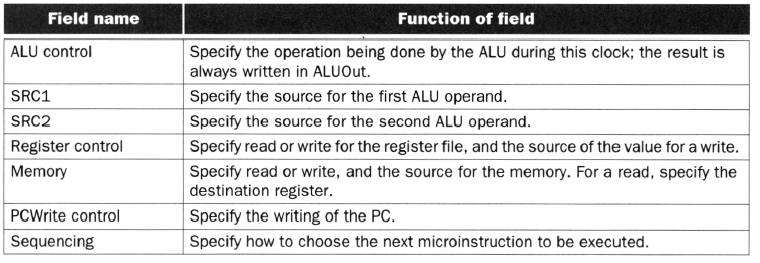

Microinstruction format |

|

|

|

|

|

Series of fields: each

field specifies set of control signals |

|

|

|

|

Signals never asserted

simultaneously may share same field |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig. 5.44 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|