|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

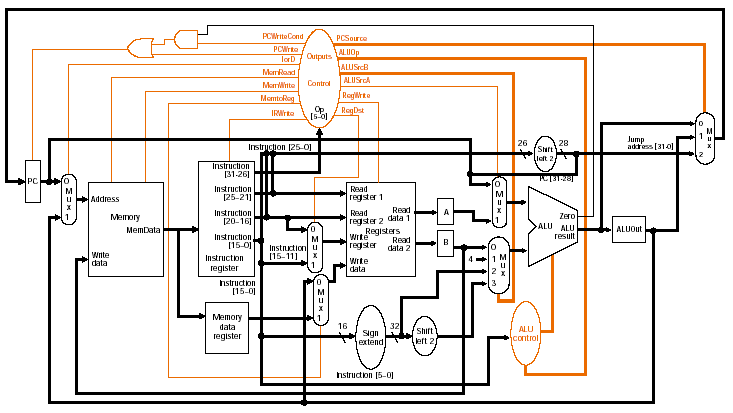

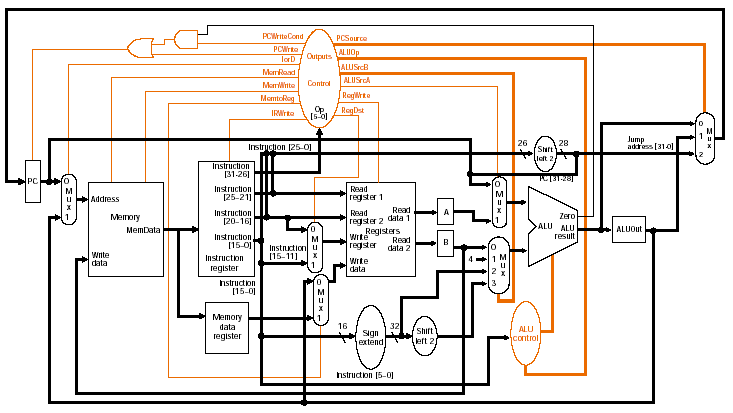

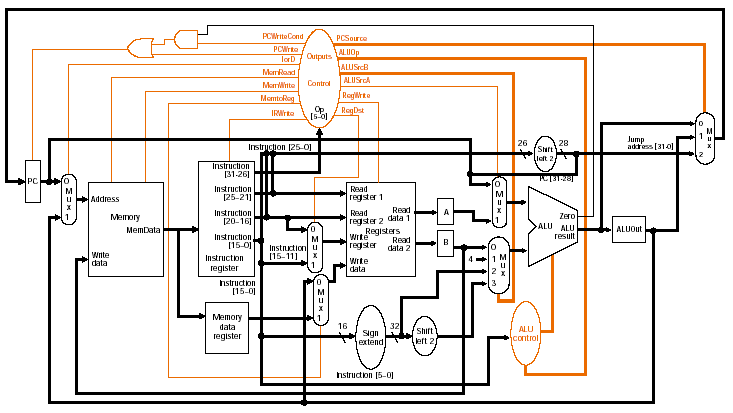

Multi-cycle datapath:

instruction fetch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig. 5.33 |

|

|

1. Fetch instruction

from memory and compute address of next sequential instruction |

|

|

Operation: |

|

|

|

|

|

IR = Memory[PC]; |

|

|

|

PC = PC + 4; |

|

|

|

|

Control signals needed |

|

|

|

|

|

|

|

MemRead, IRWrite asserted |

|

|

|

|

|

IorD set to 0 to select

PC as address source |

|

|

|

Increment PC by 4: |

|

|

|

|

|

|

ALUSrcA = 0: PC to ALU |

|

|

|

|

|

|

ALUSrcB = 01: 4 to ALU |

|

|

|

|

|

|

ALUOp = 00: add |

|

|

|

Store PC back |

|

|

|

PCSource = 00: ALU result |

|

|

|

PCWrite = 1 |

|

|

|

The memory access and PC

increment can occur in parallel. Why? |

|

|

|

Because the PC value

doesn't change until the next clock cycle! |

|

|

|

Where else is the

incremented PC value stored? |

|

|

|

|

ALUOut |

|

|

|

Does this have any other

effect? No |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|