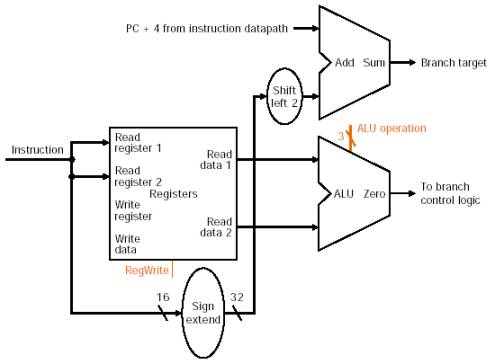

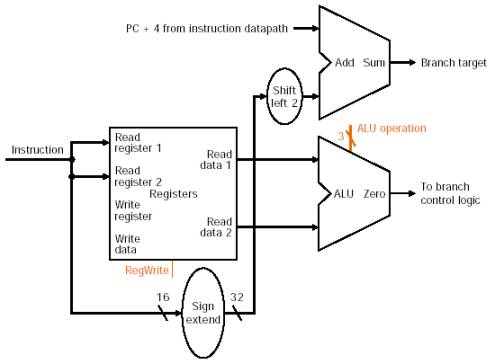

| Branch | ||||||||||||||

|

||||||||||||||

| Fig. 5.10 | ||||||||||||||

| Instruction provides read register numbers to register file, offset to sign extend | ||||||||||||||

| Registers give operand input to ALU for comparison (which ALU operation?) | ||||||||||||||

| ALU generates Zero output (what value?) to branch control | ||||||||||||||

| Sign extend provides 32-bit value to shifter, which shifts left by 2 bits | ||||||||||||||

| Adder computes branch target for possible PC update using: | ||||||||||||||

| Offset from shifter | ||||||||||||||

| PC + 4 from instruction datapath | ||||||||||||||