|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

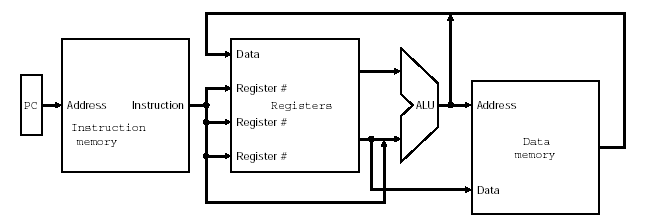

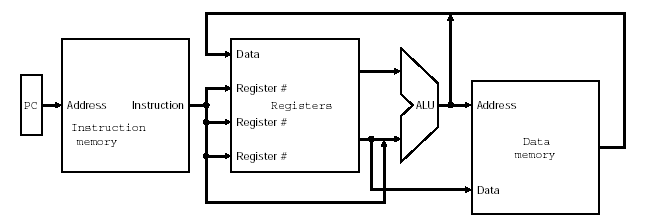

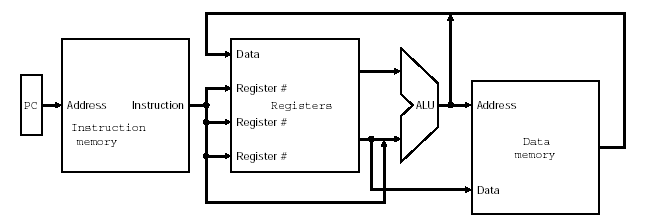

Single-cycle datapath |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig. 5.1 |

|

|

|

|

|

|

|

|

Single-cycle

implementation |

|

|

|

|

|

Assume each instruction

is executed in 1 clock cycle |

|

|

|

|

|

Each component (memory,

ALU, etc.) can be used only once |

|

|

|

|

|

Reason for assuming

separate instruction and data memories |

|

|

Advantage: simpler to

design |

|

|

|

|

|

|

Disadvantage: speed of

machine is determined by time for longest path |

|

|

|

Memory access is

much slower than register access, |

|

|

|

|

|

|

but most instructions use

only registers |

|

|

|

|

|

Better: each instruction

type can take different number of clock cycles |

|

|

Common elements for all

instructions |

|

|

|

|

|

Instruction fetch, PC

update |

|

|

|

|

|

Access 1 or 2 registers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|