|

||

| Register file: implementing | |||||||||||||||||||

| Example: register file with 4 registers | |||||||||||||||||||

| Each parallel-load register | |||||||||||||||||||

|

|||||||||||||||||||

| Input | |||||||||||||||||||

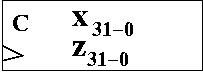

| 32-bit data, x31-0 | |||||||||||||||||||

| 1 control bit, c | |||||||||||||||||||

| clock | |||||||||||||||||||

| Output | |||||||||||||||||||

| 32-bit data, z31-0 | |||||||||||||||||||

| When c = 1, the register parallel loads, i.e., z31-0 = x31-0. | |||||||||||||||||||

| When c = 0, it holds the value. | |||||||||||||||||||

| In order to organize the registers into a register file, we need the concept of a bus: | |||||||||||||||||||

| composed of multiple wires | |||||||||||||||||||