|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

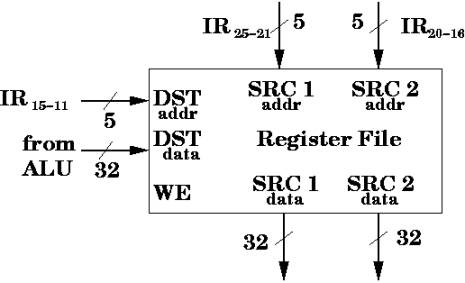

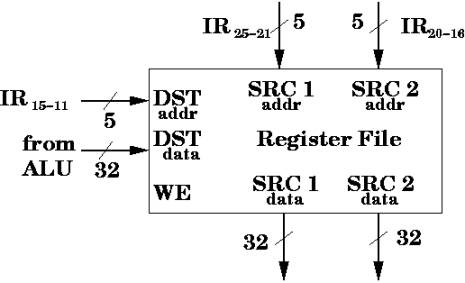

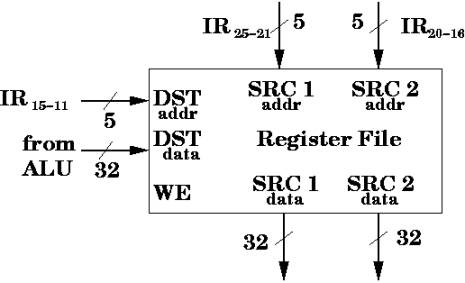

Register file: writing |

|

|

|

|

|

|

|

Reading from a register

file is only part of the story |

|

|

Writing to a register

file |

|

|

|

|

Control input called

write enable (WE) |

|

|

|

|

When WE = 1, then we want

to write to the register file |

|

|

|

|

Once we add R[2] to

R[3], we need to save the result to destination register R[1] |

|

|

|

|

Require 5 bits to

indicate the destination register (DST addr) |

|

|

|

|

|

Can come from IR: bits B15-11 are used for

destination register (R-type) |

|

|

|

|

Need 32 bits of data to

write to the register (DST data) |

|

|

|

|

|

Data comes from the

output of the ALU |

|

|

|

|

How the register file

looks now: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Summary: |

|

|

|

|

Inputs |

|

|

|

|

|

SRC 1 Addr: index of the

first source register (5 bits) |

|

|

|

|

|

SRC 2 Addr: index of the

second source register (5 bits) |

|

|

|

|

|

DST Addr: index of the

destination register (5 bits) |

|

|

|

|

|

DST Data: data to be

written to the destination register (32 bits) |

|

|

|

|

|

WE: DST Data is written

to the register at index DST Addr only when WE = 1. |

|

|

|

Outputs |

|

|

|

|

|

SRC 1 Data: contents of

the first source register, as specified by SRC 1 Addr. |

|

|

|

|

SRC 2 Data:

contents of the second source register, |

|

|

|

|

|

|

as specified by SRC 2

Addr. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|