|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

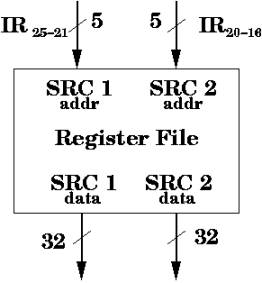

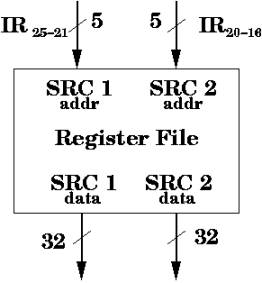

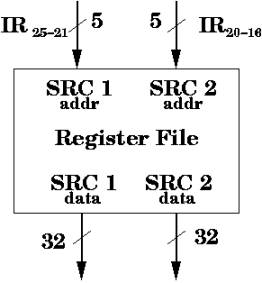

Register file: black box |

|

|

|

|

|

|

|

Encoding for the

instruction |

|

|

|

|

|

|

000000 |

00010 |

00011 |

00001 |

00000 |

100000 |

|

|

|

|

|

b31-26 |

b25-21 |

b20-16 |

b15-11 |

b10-6 |

b5-0 |

|

|

|

|

|

opcode |

$rs |

$rt |

$rd |

shamt |

function |

|

|

|

|

Good ISA design helps: |

|

|

|

|

|

Can get the desired bits

for the source registers without doing much decoding. |

|

|

|

|

Once

the ten bits are sent from the IR as ADDRESS inputs to the register file, |

|

|

|

|

|

the register file

produces 64 bits of DATA output |

|

|

|

|

Implementation as a black

box: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notice that we

haven't said anything yet about |

|

|

|

|

HOW the address inputs |

|

|

|

|

are turned into data

outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|