|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

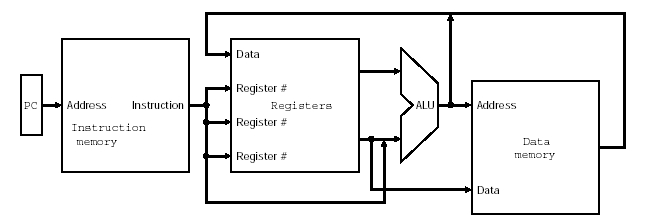

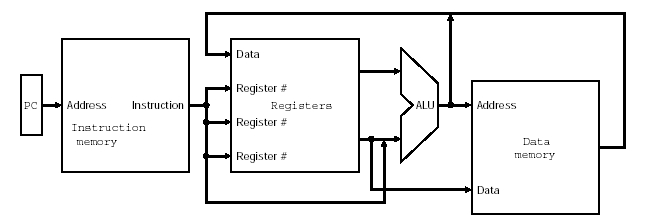

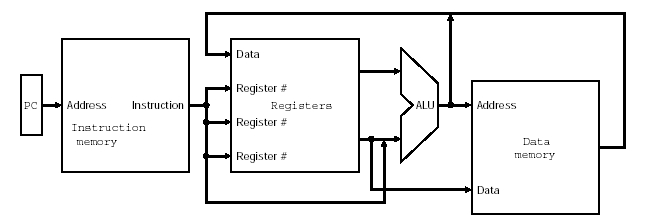

Datapath |

|

|

|

|

|

|

|

Datapath: flow of data

during instruction execution |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig. 5.1 |

|

|

|

|

|

|

|

|

|

Process |

|

|

|

|

|

|

|

PC gives address of next

instruction to (instruction) memory |

|

|

|

|

|

Memory gives instruction

contents to IR (instruction register, not shown) |

|

|

IR

gives |

|

|

|

|

|

|

|

|

Register numbers (2

source, 1 destination) to registers |

|

|

|

|

|

Immediate data to ALU |

|

|

|

|

|

|

Registers give data to |

|

|

|

|

|

|

|

ALU |

|

|

|

|

|

|

|

|

|

(Data) memory |

|

|

|

|

|

|

ALU processes operands

and gives result to |

|

|

|

|

|

Register

(arithmetic/logical result) |

|

|

|

|

|

Memory (as data address

for load or store) |

|

|

|

|

|

Data memory gives data to

registers (if load) |

|

|

|

|

What's missing from this

picture? |

|

|

|

|

|

How to update the PC? |

|

|

|

|

|

|

Could have counter to

increment, but what about branches and jumps? |

|

|

|

|

Use ALU to compute branch

address, but need more control |

|

|

|

|

|

Where do register

addresses come from? |

|

|

|

|

|

How do we control

register read/write? |

|

|

|

|

|

What about immediate

operands? |

|

|

|

|

|

How to determine what

operation for ALU to perform? |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|