| Finite state machines: counter | |||||||||||||||

| Use FSM to implement a synchronous counter | |||||||||||||||

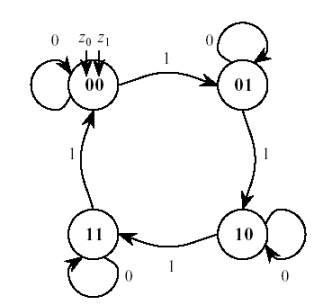

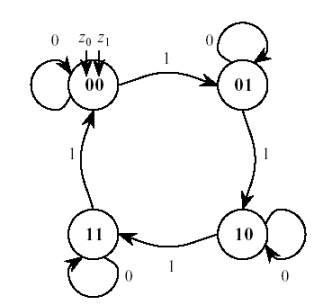

| 2-bit (mod 4) counter |

|

||||||||||||||

| starts at 00 | |||||||||||||||

| counts up to 11 | |||||||||||||||

| resets to 00 after 11 | |||||||||||||||

| Finite state machine | |||||||||||||||

| state (q): 2 bits, initially 00 | |||||||||||||||

| output (z): same as state | |||||||||||||||

| input | |||||||||||||||

| x = 0: same state | |||||||||||||||

| x = 1: increment | |||||||||||||||

| Usage | |||||||||||||||

| Keeping track of number of bits sent | |||||||||||||||

| Program counter (PC) | |||||||||||||||

| Increments each clock cycle to point to next instruction | |||||||||||||||